Datasheet

81

Networking Silicon — GD82559ER

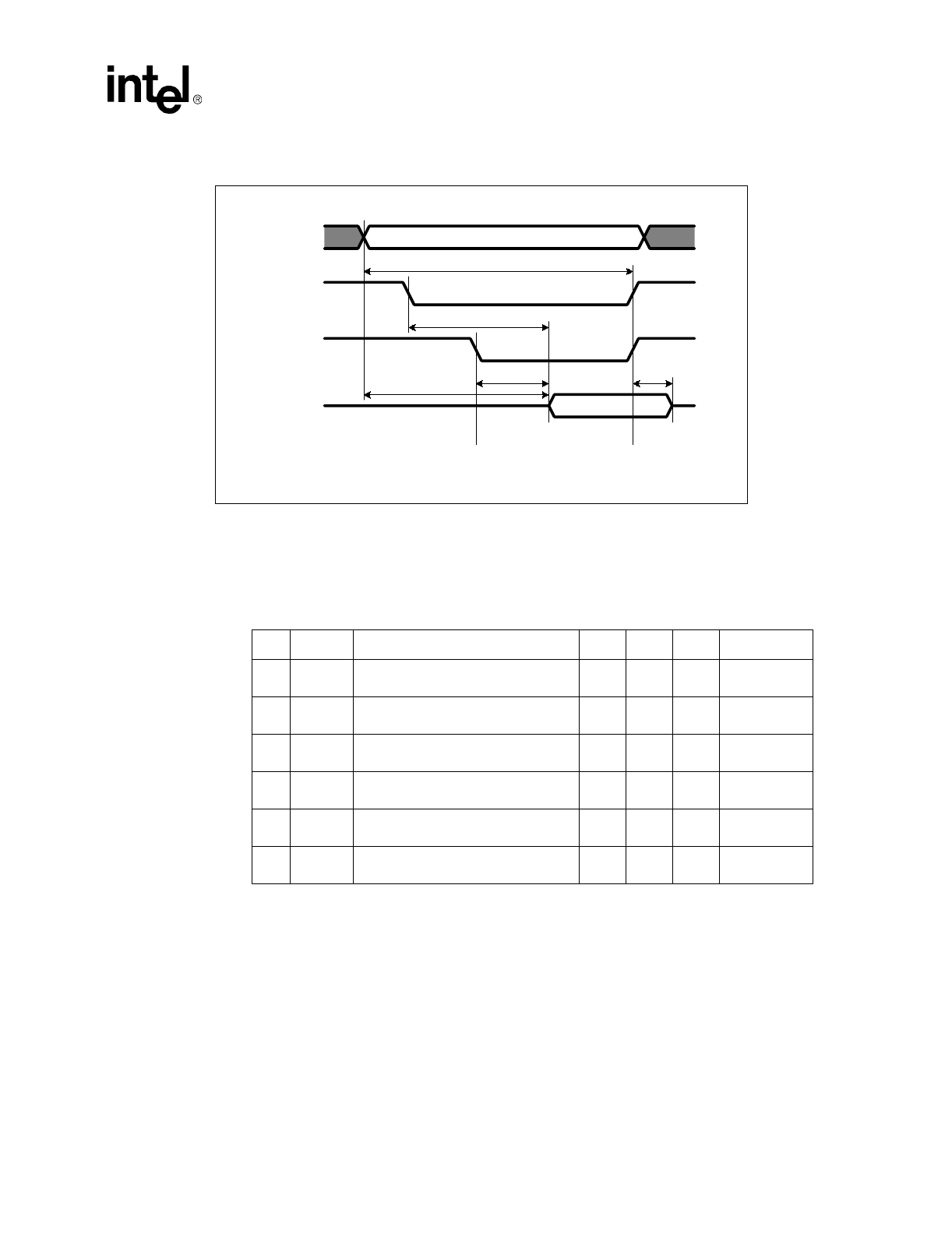

10.4.2.4 EEPROM Interface Timings

The 82559ER is designed to support a standard 64x16, or 256x16 serial EEPROM. Table 27

provides the timing parameters for the EEPROM interface signals. The timing parameters are

illustrated in Figure 30.

Figure 29. Flash Timings for a Read Cycle

FLADDR

FLCS#

FLOE#

FLDATA-R

Address Stable

Data In

T35

T37

T38 T39

T36

Table 27. EEPROM Timing Parameters

Symbol Parameter Min Max Units Notes

T50 t

EFSK

Serial Clock Frequency 1 Mhz

EEPROM fsk =

1 MHz

T51 t

ECSS

Delay from EECS High to EESK High 300 ns

EEPROM tcss

= 50 ns

T52 t

ECSH

Delay from EESK Low to EECS Low 30 ns

EEPROM tcsh

= 0 ns

T53 t

EDIS

Setup Time of EEDI to EESK 300 ns

EEPROM tdis

= 150 ns

T54 t

EDIH

Hold Time of EEDI after EESK 300 ns

EEPROM tdih

= 150 ms

T55 t

ECS

EECS Low Time 750 ns

EEPROM tcs =

250 ns