GD82559ER — Networking Silicon

60

Datasheet

8.1.8 Receive Direct Memory Access Byte Count

The Receive DMA Byte Count register keeps track of how many bytes of receive data have been

passed into host memory via DMA.

8.1.9 Early Receive Interrupt

The Early Receive Interrupt register allows the 82559ER to generate an early interrupt depending

on the length of the frame. An early interrupt is indicated by the ER bit in the SCB Status Word and

the assertion of the INTA# signal.

8.1.10 Flow Control Register

The Flow Control Register contains the following fields:

•

Flow Control Command

The Flow Control Command field describes the action of the flow control process (for

example, pause, on, or off).

•

Flow Control Threshold

The Flow Control Threshold field contains the threshold value (in other words, the number of

free bytes in the Receive FIFO).

8.1.11 Power Management Driver Register

The 82559ER provides an indication in memory and I/O space that a wake-up event has occurred.

It is located in the PMDR.

29

Interrupt Enable.

When this bit is set to 1b by software, the 82559ER asserts an interrupt to

indicate the end of an MDI cycle.

28

Ready.

This bit is set to 1b by the 82559ER at the end of an MDI transaction. It should be

reset to 0b by software at the same time the command is written.

27:26

Opcode.

These bits define the opcode: 01 for MDI write and 10 for MDI read. All other values

(00 and 11) are reserved.

25:21

PHY Address.

This field of bits contains the PHY address (Default = 00001b).

20:16

PHY Register Address.

This field of bits contains the address of the PHY Register to be

accessed.

15:0

Data.

In a write command, software places the data bits in this field, and the 82559ER

transfers the data to the PHY unit. During a read command, the 82559ER reads these bits

serially from the PHY register (specified by bits 20:16), and software reads the data from this

location.

Bits Description

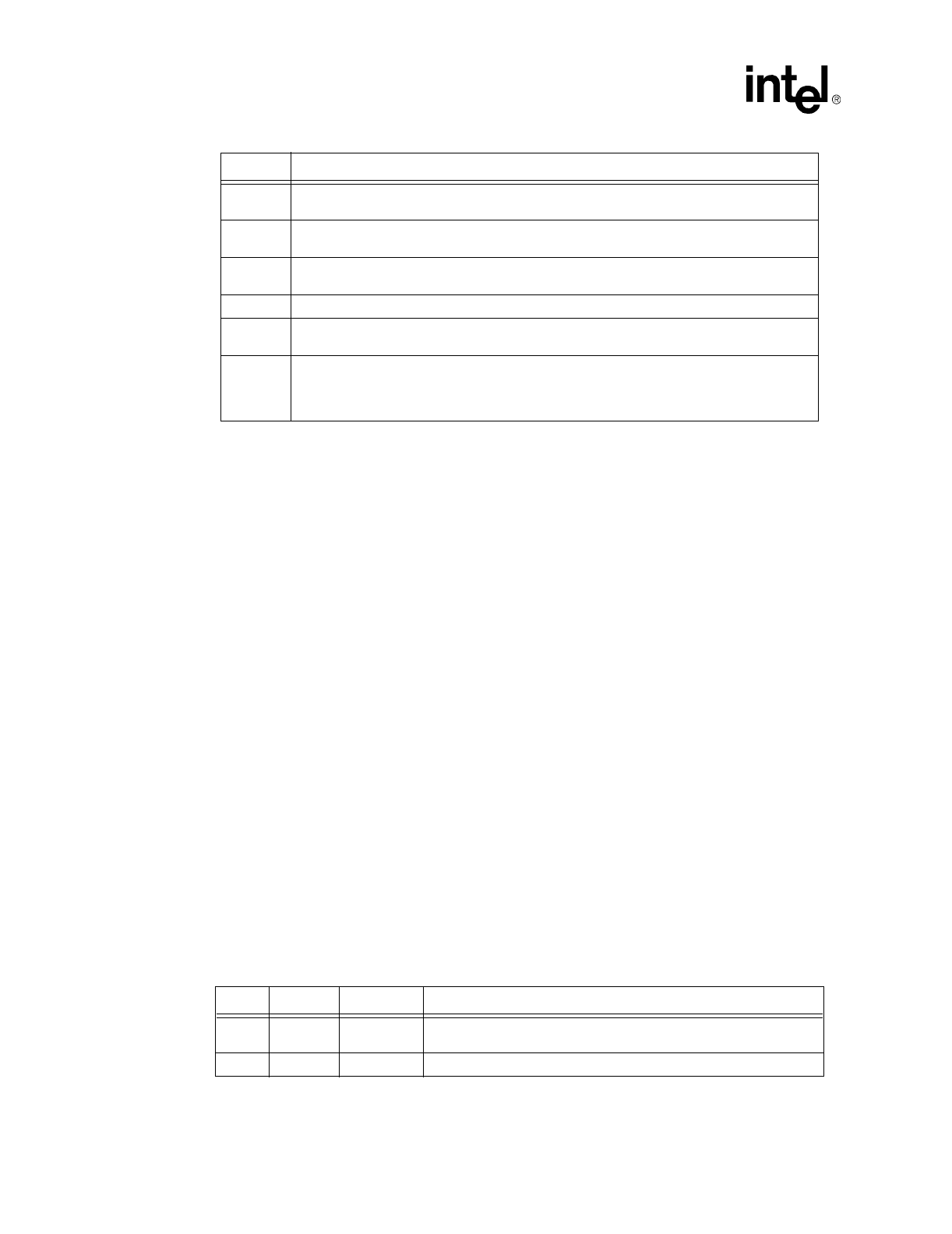

Table 11. Power Management Driver Register

Bits Default Read/Write Description

31 0b Read/Clear

Link Status Change Indication.

The link status change bit is set

following a change in link status and is cleared by writing a 1b to it.

30 0b Read

Not Supported, will always read as a ‘0’.