Datasheet

79

Networking Silicon — GD82559ER

NOTE:

Input test is done with 0.1V

CC

overdrive. V

max

specifies the maximum peak-to-peak waveform allowed

for testing input timing.

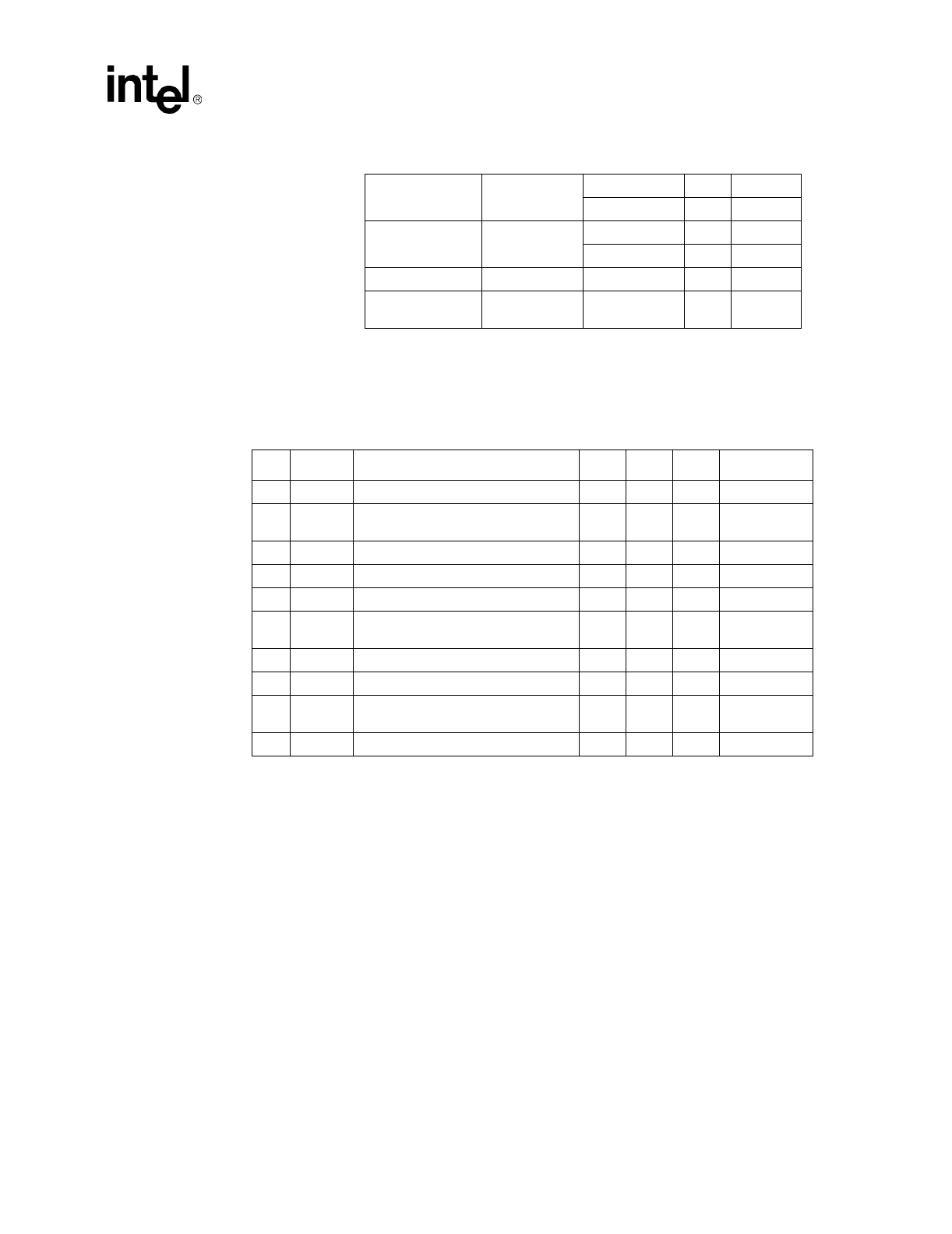

10.4.2.2 PCI Timings

NOTES:

1. Timing measurement conditions are illustrated in Figure 27.

2. PCI minimum times are specified with loads as detailed in the PCI Bus Specification, Revision 2.1, Section

4.2.3.2.

3. n a PCI environment, REQ# and GNT# are point-to-point signals and have different output valid delay times

and input setup times than bussed signals. All other signals are bussed.

4. Timing measurement conditions are illustrated in Figure 28.

5. RST# is asserted and de-asserted asynchronously with respect to the CLK signal.

6. All PCI interface output drivers are floated when RST# is active.

10.4.2.3 Flash Interface Timings

The 82559ER is designed to support up to 150 nanoseconds of Flash access time. The V

PP

signal in

the Flash implementation should be connected permanently to 12 V. Thus, writing to the Flash is

controlled only by the FLWE# pin.

Table 26 provides the timing parameters for the Flash interface signals. The timing parameters are

illustrated in Figure 29.

V

step

(rising edge) 0.285V

CC

0.325V

CC

V Min Delay

0.475V

CC

V Max Delay

V

step

(falling edge) 0.615V

CC

0.475V

CC

V Min Delay

0.325V

CC

V Max Delay

V

max

0.4V

CC

0.4V

CC

V

Input Signal Edge

Rate

11V/ns

Table 24. Measure and Test Condition Parameters

Table 25. PCI Timing Parameters

Symbol Parameter Min Max Units Notes

T14 t

val

PCI CLK to Signal Valid Delay 2 11 ns 1, 2, 4

T15 t

val(ptp)

PCI CLK to Signal Valid Delay (point-

to-point)

212ns 1, 2, 4

T16 t

on

Float to Active Delay 2 ns 1

T17 t

off

Active to Float Delay 28 ns 1

T18 t

su

Input Setup Time to CLK 7 ns 4, 5

T19 t

su(ptp)

PCI Input Setup Time to CLK (point-to-

point)

10 ns 4, 5

T20 t

h

Input Hold Time from CLK 0 ns 6

T21 t

rst

Reset Active Time After Power Stable 1 ms 6

T22 T

rst-clk

PCI Reset Active Time After CLK

Stable

100 µs6

T23 T

rst-off

Reset Active to Output Float Delay 40 ns 6, 7