IntelP®P Server Board S3420GP TPS Design and Environmental Specifications

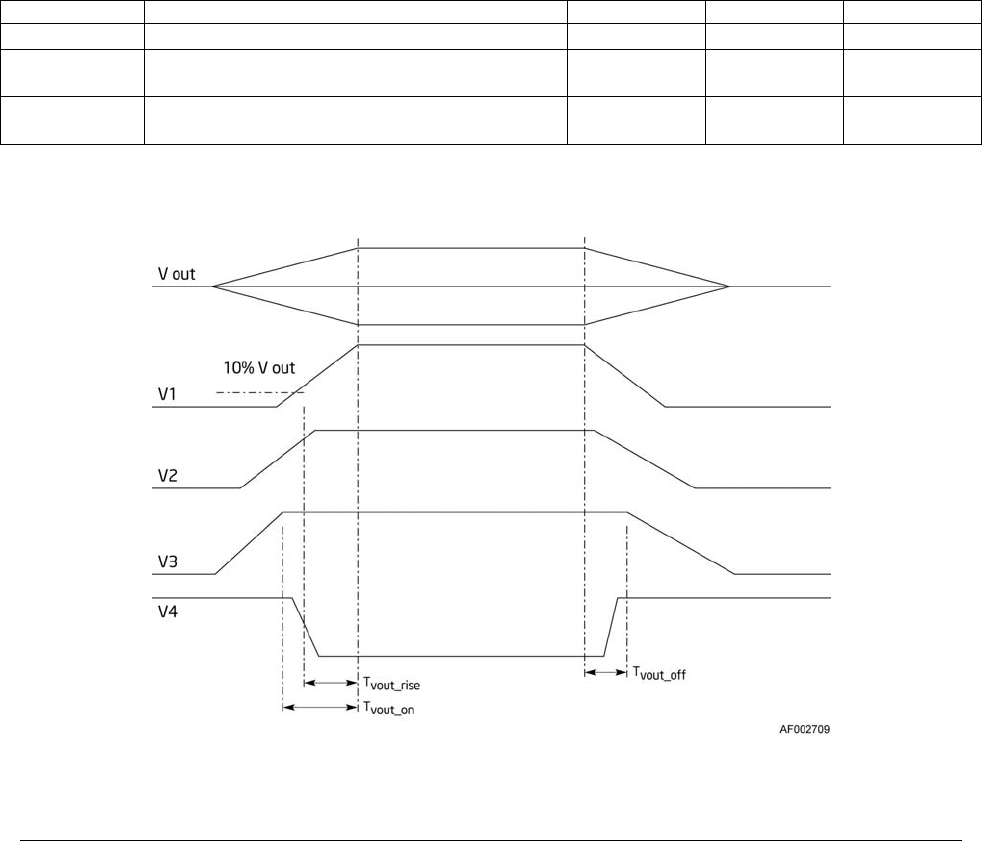

The output voltages must rise from 10% to within regulation limits (T

vout_rise

) within 5 ms

to 70 ms, except for 5 VSB, in which case it is allowed to rise from 1.0 ms to 25 ms.

The +3.3 V, +5 V, and +12 V output voltages should start to rise approximately at the

same time.

All outputs must rise monotonically.

The +5 V output must be greater than the +3.3 V output during any point of the voltage

rise.

The +5 V output must never be greater than the +3.3 V output by more than 2.25 V.

Each output voltage should reach regulation within 50 ms (T

vout_on

) of each other when

the power supply is turned on.

Each output voltage should fall out of regulation within 400 msec (T

vout_off

) of each other

when the power supply is turned off.

Figure 37 and Figure 38 shows the timing requirements for the power supply being turned on

and off via the AC input with PSON held low and the PSON signal with the AC input applied.

Table 62. Output Voltage Timing

Item Description Minimum Maximum Units

T

vout_rise

Output voltage rise time from each main output. 5.0

1

70

1

Msec

T

vout_on

All main outputs must be within regulation of each

other within this time.

50 Msec

T

vout_off

All main outputs must leave regulation within this

time.

700 Msec

Note:

1. The 5 VSB output voltage rise time should be from 1.0 ms to 25.0 ms.

Figure 37. Output Voltage Timing

Revision 1.0

Intel order number E65697-003

91