Design and Environmental Specifications IntelP®P Server Board S3420GP TPS

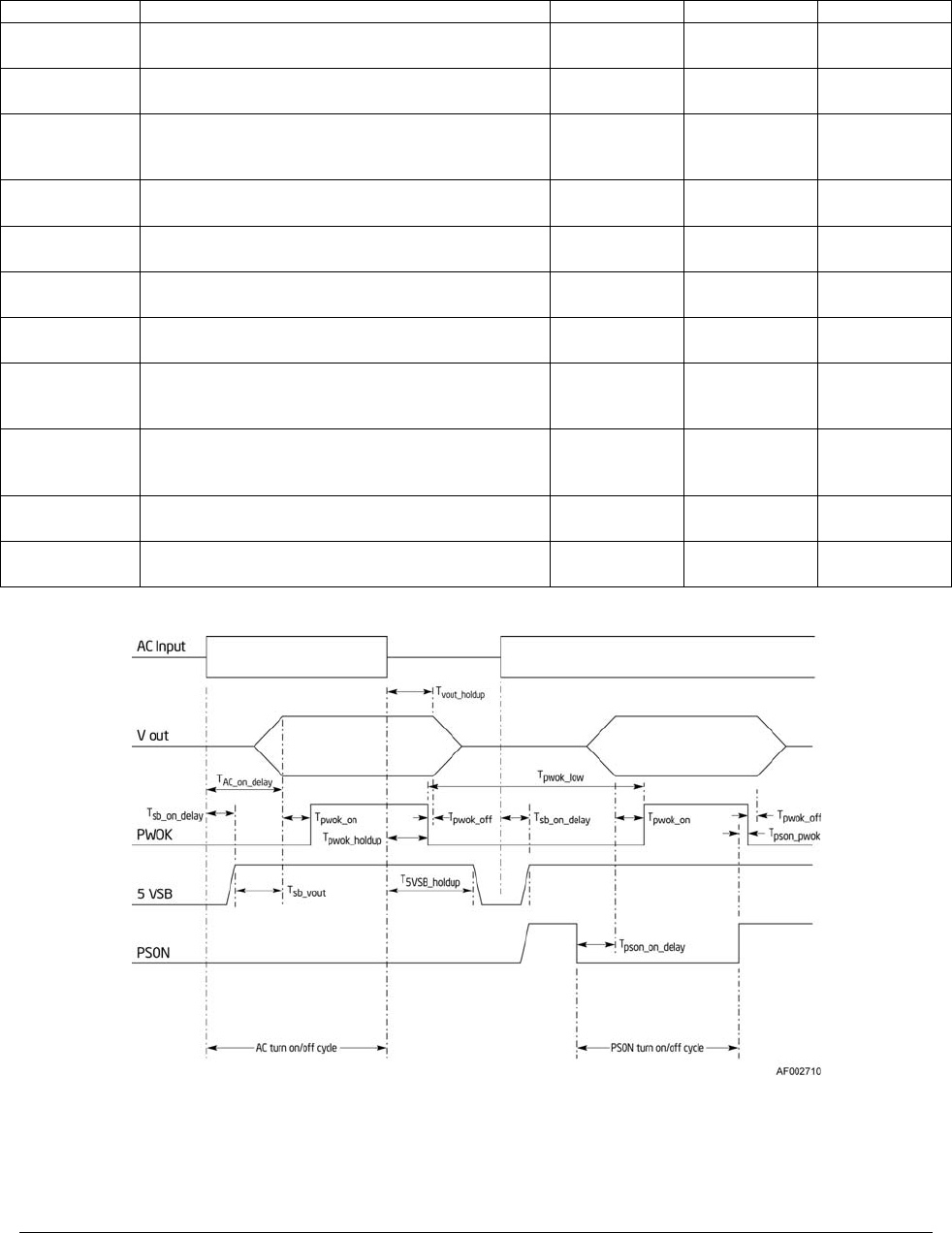

Table 63. Turn On/Off Timing

Item Description Minimum Maximum Units

T

sb_on_delay

Delay from AC being applied to 5 VSB being

within regulation.

N/A 1500

Msec

T

ac_on_delay

Delay from AC being applied to all output voltages

being within regulation.

N/A 2500

Msec

T

vout_holdup

Duration for which all output voltages stay within

regulation after loss of AC. Measured at 80% of

maximum load.

21 N/A

Msec

T

pwok_holdup

Delay from loss of AC to de-assertion of PWOK.

Measured at 80% of maximum load.

20 N/A

Msec

T

pson_on_delay

Delay from PSON

#

active to output voltages within

regulation limits.

5 400

Msec

T

pson_pwok

Delay from PSON

#

deactive to PWOK being de-

asserted.

N/A 50

Msec

T

pwok_on

Delay from output voltages within regulation limits

to PWOK asserted at turn on.

100 500

Msec

T

pwok_off

Delay from PWOK de-asserted to output voltages

(3.3 V, 5 V, 12 V, -12 V) dropping out of regulation

limits.

1 N/A

Msec

T

pwok_low

Duration of PWOK being in the de-asserted state

during an off/on cycle using AC or the PSON

signal.

100 N/A

Msec

T

sb_vout

Delay from 5 VSB being in regulation to O/Ps

being in regulation at AC turn on.

50 1000

Msec

T

5VSB_holdup

Duration for which the 5 VSB output voltage stays

within regulation after loss of AC.

70 N/A

Msec

Figure 38. Turn On/Off Timing (Power Supply Signals)

Revision 1.0

Intel order number E65697-003

92