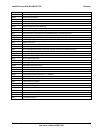

IntelP®P Server Board S3420GP TPS Appendix D: POST Code Errors

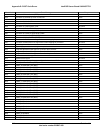

Error Code Error Message Response

0xA500 ATA/ATPI ATA bus SMART not supported. No Pause

0xA501 ATA/ATPI ATA SMART is disabled. No Pause

0xA5A0 PCI Express* component encountered a PERR error. No Pause

0xA5A1 PCI Express* component encountered a SERR error. Halt

0xA5A4 PCI Express* IBIST error. Pause

0xA6A0 DXE boot services driver Not enough memory available to shadow a legacy option ROM. No Pause

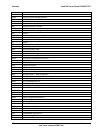

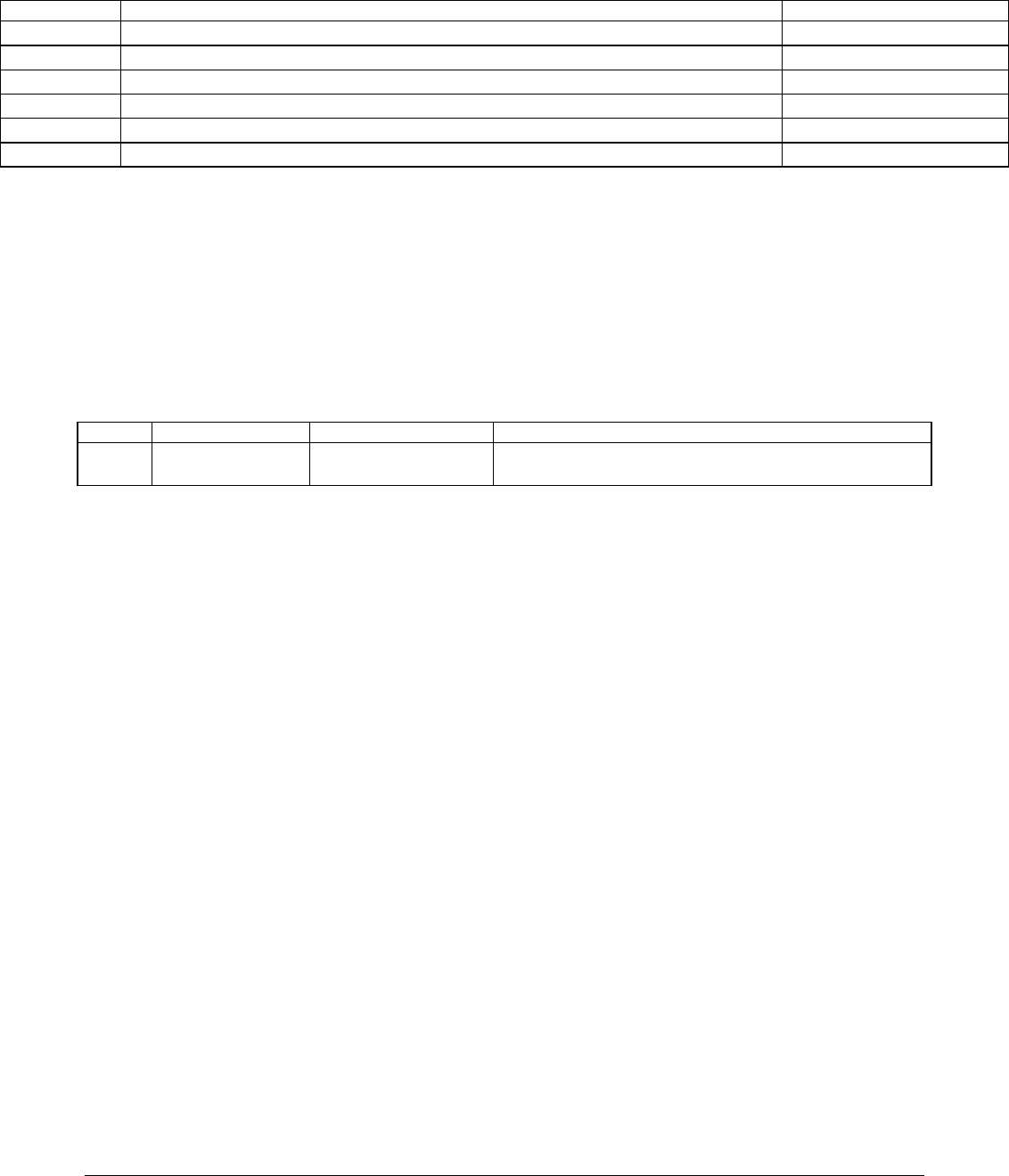

POST Error Beep Codes

The following table lists POST error beep codes. Prior to system video initialization, the BIOS

uses these beep codes to inform users on error conditions. The beep code is followed by a

user-visible code on POST Progress LEDs.

Table 70. POST Error Beep Codes

Beeps Error Message POST Progress Code Description

3 Memory error Multiple System halted because a fatal error related to the memory

was detected.

Revision 1.0

Intel order number E65697-003

117