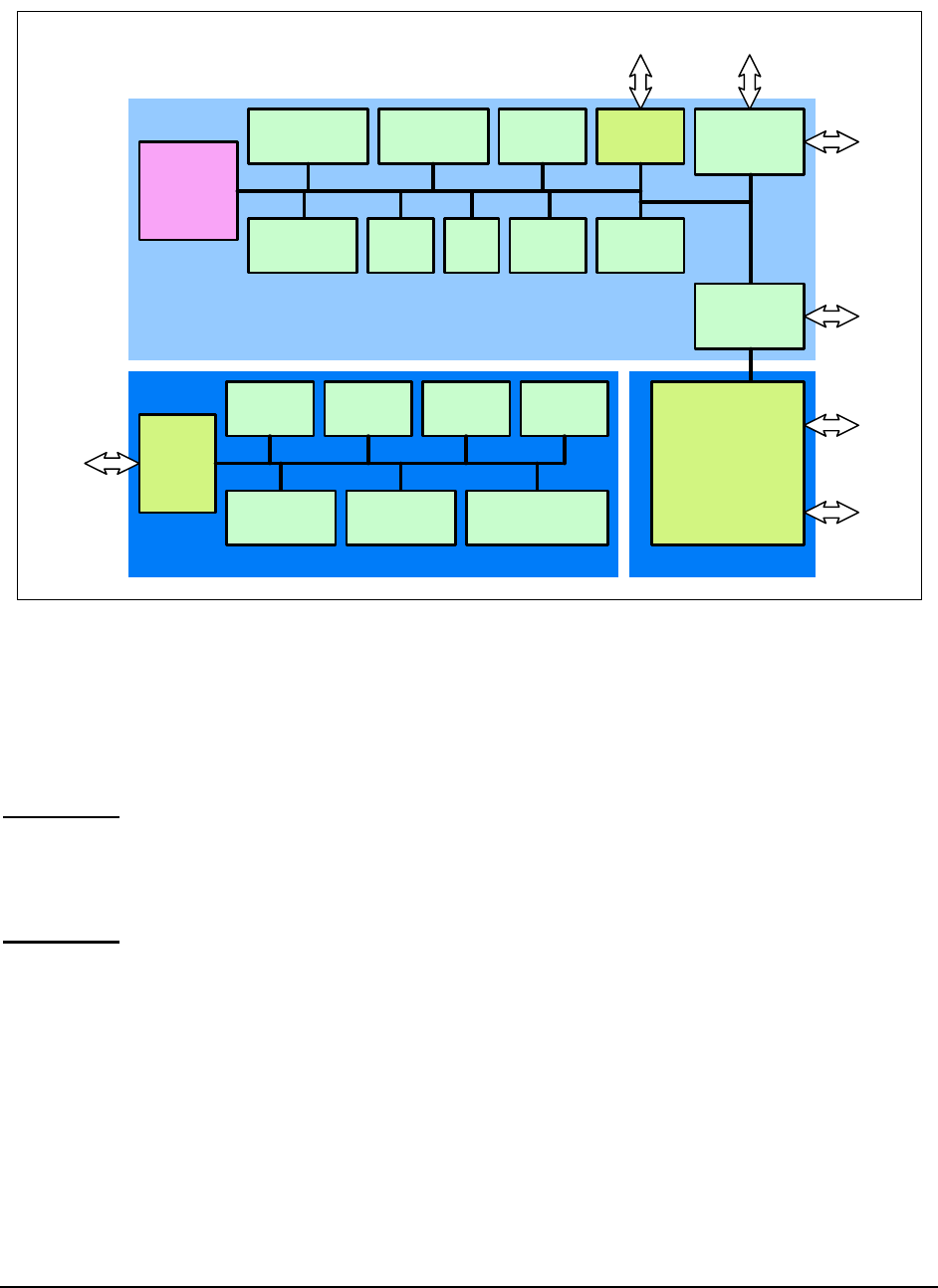

IntelP®P Server Board S3420GP TPS Functional Architecture

ARM926EJ-S

16K D & I

Cache

Interrupt

Controller

Fan Tach (12)

PWM (4)

ADC

Thermal

USB 1.1

&

USB 2.0

LPC Master,

JTAG Master,

& SPI FLash

UART (3) GPIO

KCS

BT &

Mailboxes

System

Wakeup

Control

LPC

Interface

Graphics

Controller

BMC & KVMS Subsystem

BMC & KVMS Subsystem Graphics Subsystem

RTC &

General Purpose

TImers (3)

UART

(3)

I2C

(6)

Ethernet

MAC with

RMII (2)

Crypto

Accelerator

DDR-II

16-bit

Memory

Controller

LPC to SPI

Flash Bridge

Watchdog

Timer

Real Time Clock

Interface

(external RTC)

LPC

Interface

To Host

Video

Output

PCIe x1

Interface

DDR-II

(up to

667MHz)

er

Figure 13. Integrated BMC Hardware

3.6.1 Integrated BMC Embedded LAN Channel

The Integrated BMC hardware includes two dedicated 10/100 network interfaces.

Interface 1:

Code

Memory

USB

to Host

Integrated BMC Block Diagram

JTAG

Mast

This interface is available from either of the available NIC ports in system that can

be shared with the host. Only one NIC may be enabled for management traffic at any time. To

change the NIC enabled for management traffic, please use the “Write LAN Channel Port” OEM

IPMI command. The default active interface is port 1 (NIC1).

Interface 2: This interface is available from the optional RMM3 which is a dedicated

management NIC that is not shared with the host.

For these channels, support can be enabled for IPMI-over-LAN and DHCP.

For security reasons, embedded LAN channels have the following default settings:

IP Address: Static

All users disabled

3.6.2 Optional RMM3 Advanced Management Board

On the Intel

®

Server Board S3420GPLX provides RMM3 module. RMM3 advanced

management board serves two purposes:

Revision 1.0

Intel order number E65697-003

25