Connector/Header Locations and Pin-outs IntelP®P Server Board S3420GP TPS

2 SGPIO Load Signal SGPIO_LOAD

3 SGPIO_DATAOUT0 S IO DaGP ta Out

4 SGPIO_DATAOUT1 S IO DaGP ta In

6.4 Front Control Panel Connector

The server board provides a 24-pin SSI front panel connector (J1C1) for use with Intel

®

and

third-party chassis. The following table provides the pin-out for this connector.

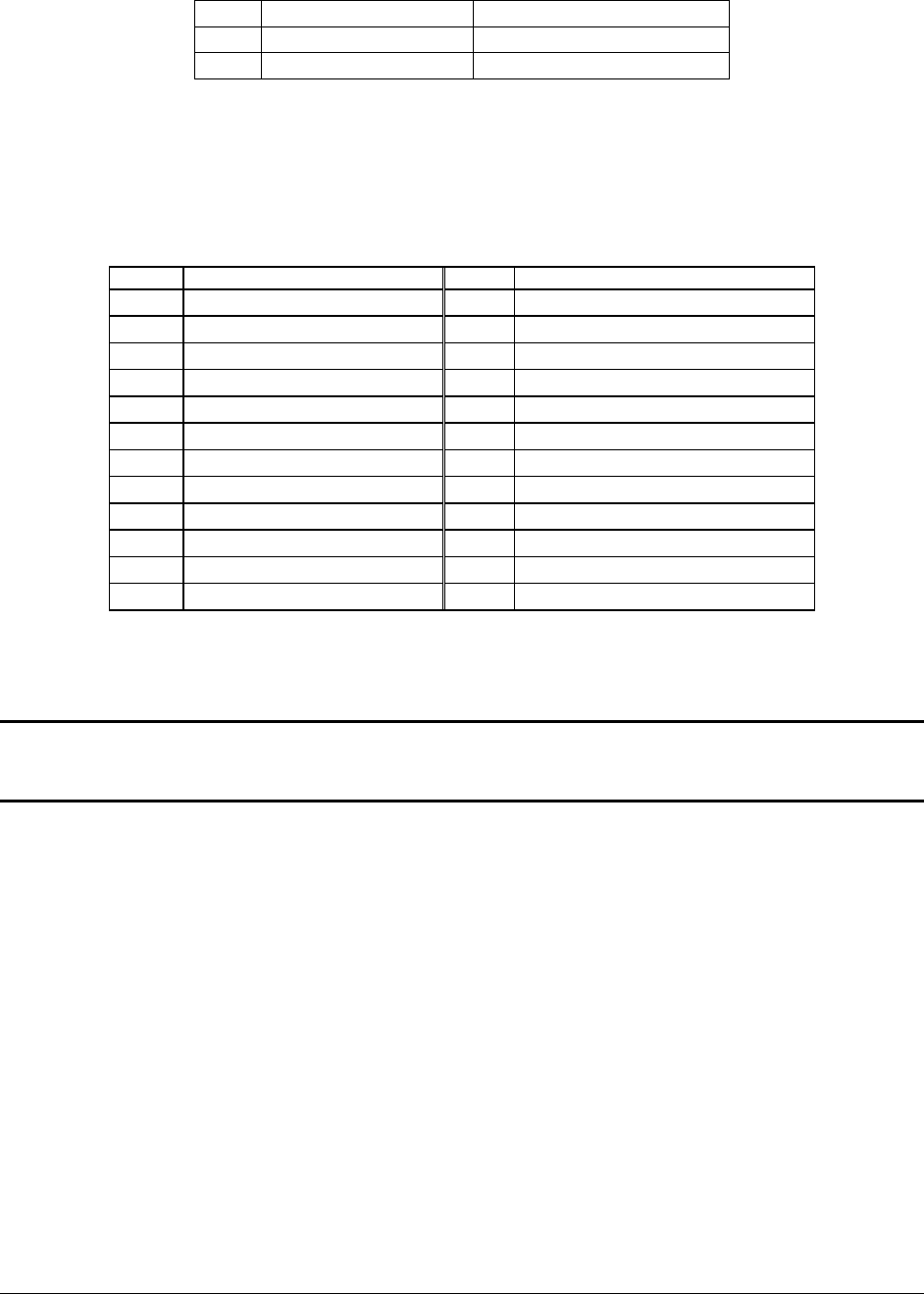

Table 38. Front Panel SSI Standard 24-pin Connector Pin-out (J1C1)

Pin Signal Name Pin Signal Name

1 2 P3V3P3V3_AUX _AUX

3 Key 4 P5V_STBY

5 FP_PWR_LED_N 6 FP_ID_LED_N

7 P3V3 8 LED_GREEN_R_N

9 LED_HDD_ACTIVITY_N 10 LED_AMBER_R_N

11 FP_PWR_BTN_N 12 LED_NIC1_ACT_R

13 GND 14 LED_NIC1_LINK_FP_N

15 RST_FP_BTN_N 16 SMB_SENS_DAT

17 ND 18 SMB_SENSOR_CLK G

19 FP_ID_BTN_N INTRU_HDR_N 20

21 PU_ SORFM_SIO_TEMP_SEN 22 LED_NIC2_ACT_R

23 FP_NMI_BTN_N 24 LED_NIC2_LINK_FP_N

Combined system BIOS and the Integrated BMC support provide the functionality of the various

supported control panel buttons and LEDs. The following sections describe the supported

functionality of each control panel feature.

through the bridge board connector at location Note: Control panel features are also routed

J1C1 as is implemented in Intel Server Systems configured using a

swap backplane.

®

bridge board and a hot-

6.4.1 Power Button

The BIOS supports a front control panel power button. Pressing the power button initiates a

request that the Integrated BMC forwards to the ACPI power state machines in the chipset. It is

monitored by the Integrated BMC and does not directly control power on the power supply.

Power B tton

The Integrated BMC monitors the power button and the wake-up event signals from the

chipset. A transition from either source results in the Integrated BMC starting the power-

up sequence. Since the processor are not executing, the BIOS does not participate in

this sequence. The hardware receives the power good and reset signals from the

Integrate BMC ns t

Power Button — On to Off (Operating sy

The System Control Interrupt (SCI) is masked. The BIOS sets up the power button event

te. The Integrated BMC monitors

u — Off to On

d and then transitio o an ON state.

stem absent)

to generate an SMI and checks the power button status bit in the ACPI hardware

registers when an SMI occurs. If the status bit is set, the BIOS sets the ACPI power

state of the machine in the chipset to the OFF sta

Revision 1.0

Intel order number E65697-003

68