ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 28

The PCI datapath block contains the multiplexors and registers to steer the data to and from the PCI interfaces. The

data is de-multiplexed from the external PCI interface to the internal master and slave busses. Control logic from the

master and slave devices control the datapath.

The SSA7785 ThunderBird Avenger™ is considered a multi-function device since the operating system may wish to

load different drivers for certain functions. These functions are the audio subsystem, the joystick and the 16650 UART.

Each of these major functions must have a separate PCI configuration space. The standard PCI configuration header

for these three functions are supported in the PCI interface.

The SSA7785 ThunderBird Avenger™ PCI interface responds to and initiates PCI cycles with positive decoding

according to the PCI 2.1 specification. The interface asserts DEVSEL# after the first clock following FRAME# making it

a medium responder. For specific LAM cycles, the SSA7785 ThunderBird Avenger™ will be a fast responder. SSA7785

ThunderBird Avenger™ indicates which cycles the PCI interface responds to or initiates.

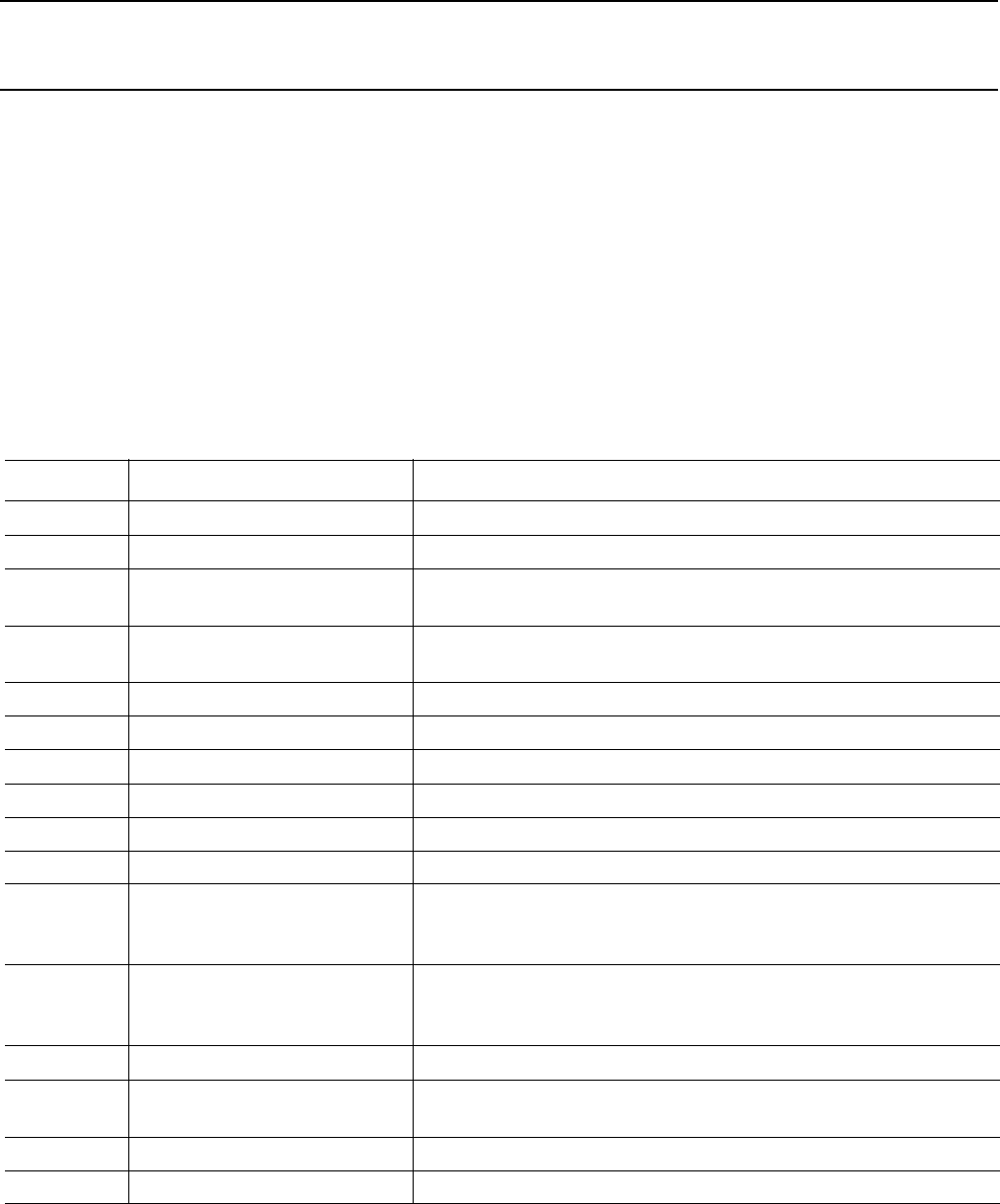

TABLE 5 PCI Bus Command Definitions and SSA7785 ThunderBird Avenger™ Responses

The SSA7785 ThunderBird Avenger™ will respond to byte, word, tri-byte or double word access for configuration read

and configuration write cycles provided PCI addressing rules are followed. Byte and word width accesses allowed for

I/O cycles depend largely on the target I/O device. In general, 24-bit and 32-bit accesses are not allowed to I/O devices

and will result in a target abort. The SSA7785 ThunderBird Avenger™ performs double word accesses when initiating

c/be#[3:0] Command Type SSA7785 ThunderBird Avenger™ Response to Cycle

0000 Interrupt Acknowledge This cycle is not claimed.

0001 Special Cycle This cycle is not claimed.

0010 I/O Read All I/O Read cycles directed to the SSA7785 ThunderBird

Avenger™ are claimed by the target interface.

0011 I/O Write All I/O Write cycles directed to the SSA7785 ThunderBird

Avenger™ are claimed by the target interface.

0100 Reserved This cycle is not claimed.

0101 Reserved This cycle is not claimed.

0110 Memory Read This cycle is not claimed.

0111 Memory Write This cycle is not claimed.

1000 Reserved This cycle is not claimed.

1001 Reserved This cycle is not claimed.

1010 Configuration Read All Configuration Read cycles are claimed by the target interface

provided IDSEL is sampled asserted during the address/cmd

phase.

1011 Configuration Write All Configuration Write cycles are claimed by the target interface

provided IDSEL is sampled asserted during the address/cmd

phase.

1100 Memory Read Multiple This cycle is not claimed.

1101 Dual Address Cycle The SSA7785 ThunderBird Avenger™ supports 32-bit

addresses only.

1110 Memory Read Line This cycle is not claimed.

1111 Memory Write and Invalidate This cycle is not claimed.