ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 66

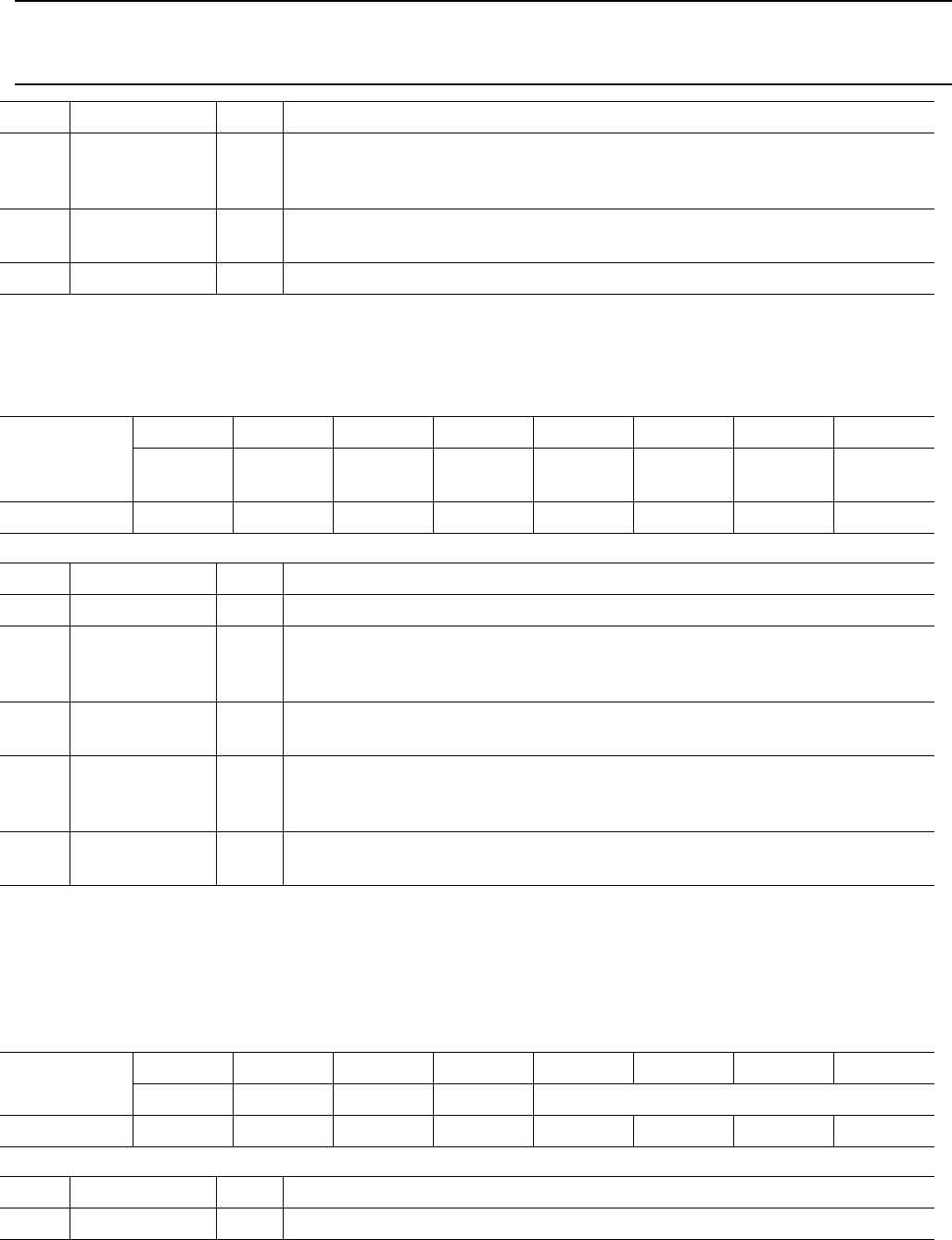

MULTIMEDIA TIMER I/O SPACE REGISTERS

TABLE 70 TMSTAT (RW/RO) - MULTIMEDIA TIMER STATUS REGISTER

MULTIMEDIA TIMER COUNT REGISTERS

There are three registers required to hold the timer value. These three registers can be read at different cycles, It is rec-

ommended that the least significant byte be read first for the most accuracy.

TABLE 71 TMCOUNT2 (RW/RO) - MULTIMEDIA TIMER COUNT REGISTER 2

2 FSTCLK RW Fast Clock Enable. When set, the timer counter will use the CCLK clock

instead of the 570 ns clock. This function will reduce the simulation and test

time of the device.

1 TMRRST RW Timer Reset. When set, this bit holds the multimedia timer in reset. The mul-

timedia timer is also reset by the system reset.

0 R RO Reserved. This bit returns a zero.

SONGBASE D7 D6 D5 D4 D3 D2 D1 D0

Offset 00h

RRRRTPLDTRE-

SUME

TMINT TINTEN

POR Value 00000000

Bit Name R/W Function

7:4 R RO Reserved. These bits return zeros.

3 TPLD RW Timer Preload Indicator. When set, this indicates the timer will start counting

from the values set in the timer count registers. When cleared, the timer will

start counting from zero or its last value when stopped

2 TRESUME RW Timer Resume. When set, the timer will resume counting at the next 570 ns

clock edge. When cleared, the timer will stop counting.

1 TMINT WC Timer Interrupt. When asserted, the multimedia timer has flagged an inter-

rupt when the timer has counted to zero. The timer will continue to count.

Writing a one to this bit will clear the interrupt.

0 TINTEN RW Timer Interrupt Enable. When set, the multimedia timer will generate an inter-

rupt.

SONGBASE D7 D6 D5 D4 D3 D2 D1 D0

Offset 03h RRRR TMCOUNT2[7:0]

POR Value 00000000

Bit Name R/W Function

7:4 R RO Reserved. These bits return zeros.

Bit Name R/W Function