ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 63

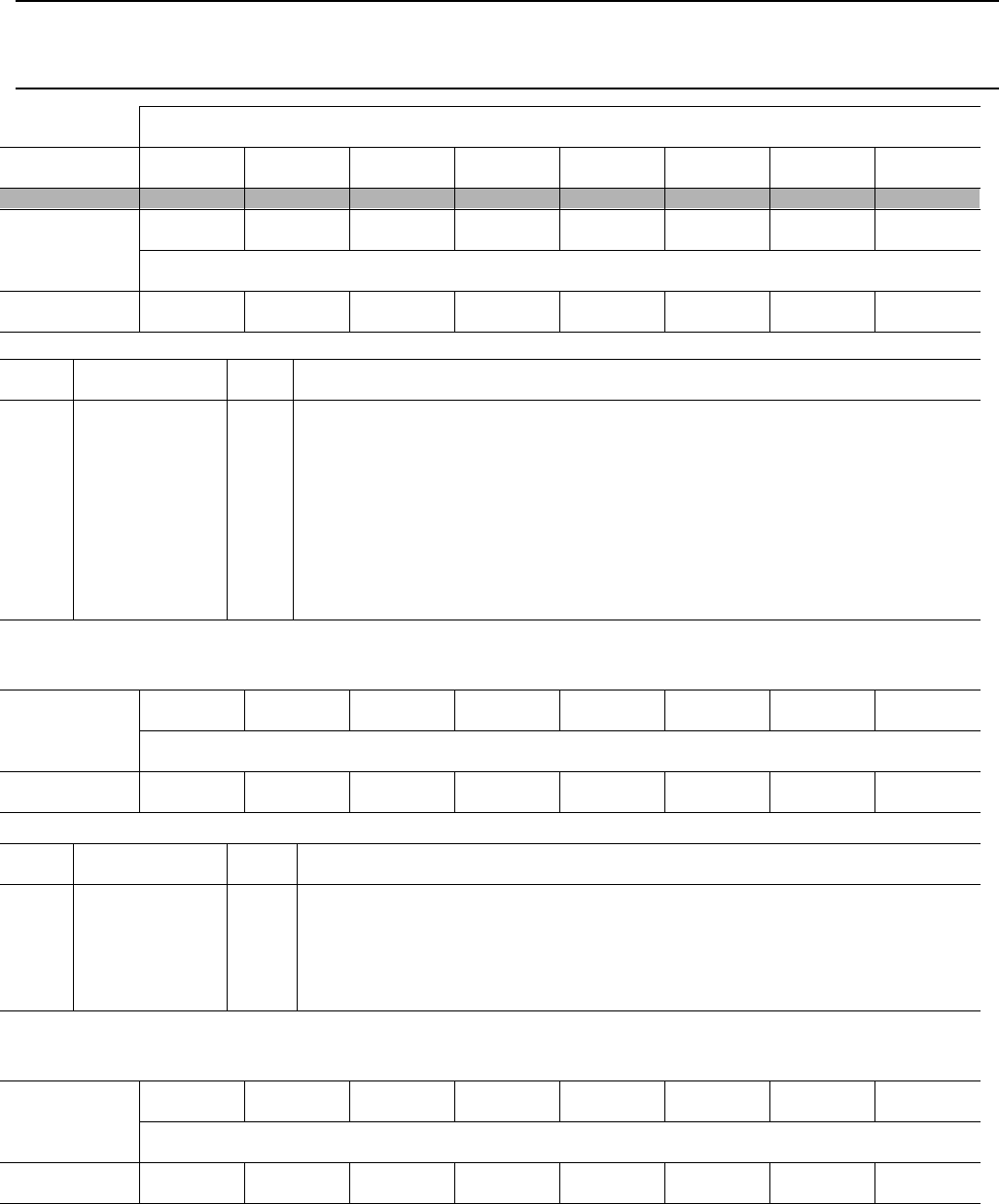

TABLE 65 Interrupt Line Register - INTLINE (RO)

TABLE 66 Interrupt Pin Register - INTPIN (RO)

Offset 2Eh

SUBSYS_ID[15:8]

POR Value

00000011

D7 D6 D5 D4 D3 D2 D1 D0

SUBSYS_ID[7:0]

POR Value

00000110

Bit Name R/W Function

15:0 SUBSYS_ID RO Subsystem ID. The Subsystem ID register allows the manufacturer to

uniquely identify their board since more than one board OEM may use the

SSA7785 ThunderBird Avenger™ chip. The Subsystem ID register is loaded

by an external EEPROM via the Serial Configuration Port after reset and

before any access to the PCI configuration header. The PCI target logic

should force a retry if the Subsystem ID register has not completed loading.

The Subsystem ID is read only to the PCI interface. If no external EEPROM is

present, then the default Subsystem ID is 0306h, identical to the SSA7785

ThunderBird Avenger™ function 2 Device ID.

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 3Ch

INTLINE[7:0]

POR Value

00000000

Bit Name R/W Function

7:0 INTLINE RO Interrupt Line. The Interrupt Line register is an eight bit register used to com-

municate interrupt line routing information. The value in this register tells

which input of the system interrupt controller(s) the SSA7785 ThunderBird

Avenger™ Device's interrupt pin is connected to. It is set to 00h to use func-

tion 0’s interrupt line. There is no legacy interrupt support for function 2.

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 3Dh

INTPIN[7:0]

POR Value

00000000