ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 52

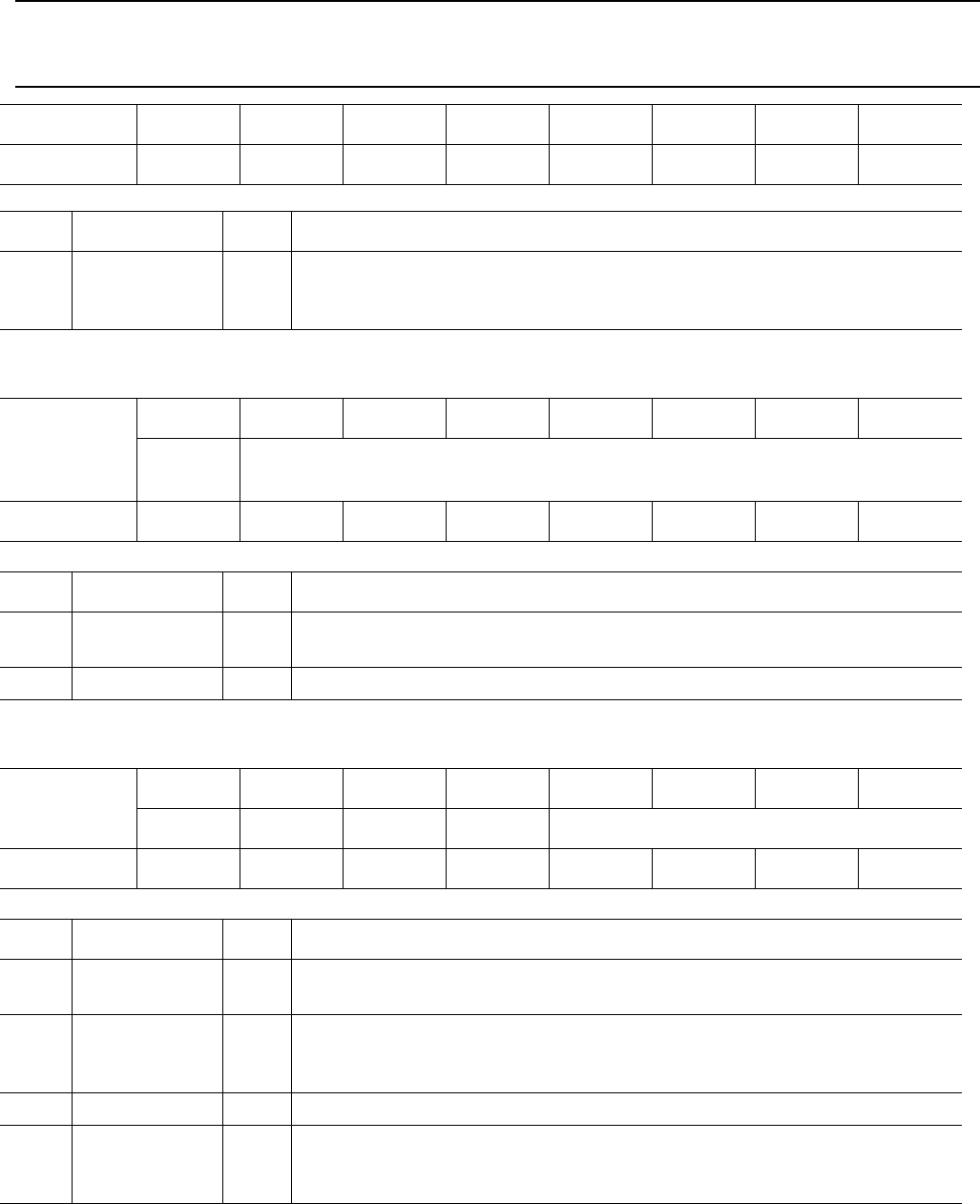

TABLE 42 Header Type Register - HEADER (RO)

TABLE 43 BIST Register - BIST (RO)

SSA7785 ThunderBird Avenger™ CFG Space 1 Legacy Base Address Registers

POR Value

00000000

Bit Name R/W Function

7:0 LATIME RO The primary bus latency timer specifies the number of primary clocks that the

primary master may consume. It is set to zero since the joystick is a target

only.

PCI CFG 1D7D6D5D4D3D2D1D0

Offset 0Eh

MULTI_

FN

HEADER[6:0]

POR Value

10000000

Bit Name R/W Function

7MULTI_FNROFor the SSA7785 ThunderBird Avenger™, function 1, this bit has no mean-

ing.

6:0 HEADER RO Header Type. A 00h indicates this device is not a PCI-to-PCI bridge.

PCI CFG 1D7D6D5D4D3D2D1D0

Offset 0Fh

BIST START R R CODE[3:0]

POR Value

00000000

Bit Name R/W Function

7 BIST RO BIST capable. BIST is not supported in the SSA7785 ThunderBird

Avenger™, function 1 at this revision.

6 START RO If BIST capable, this bit will start the BIST. Writing a 1 will start the test and

the BIST should write this bit to a zero when complete. Software should fail

the device if the BIST is not complete after 2 seconds.

5:4 R RO Reserved. These bits always return zero.

3:0 CODE RO Completion Code. A value of zero means the device has passed its test.

Non-zero values means the device has failed using device specific failure

codes.

PCI CFG 1D7D6D5D4D3D2D1D0