ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 29

master cycles. Note that the SSA7785 ThunderBird Avenger™ cannot initiate a master cycle to itself. SSA7785 Thun-

derBird Avenger™ summarizes the access rules for configuration and I/O cycles.

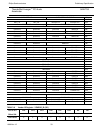

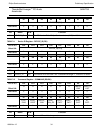

TABLE 6 BIT Width Device Access Rules

The PCI interface consists of three major blocks, the PCI master interface, the PCI slave interface and the PCI datap-

ath. The PCI master interface contains the master state machine, the master control logic, and the PM bus arbiter. The

PCI slave interface contains the target state machine, the target control logic and configuration register headers. The

PCI datapath is the de-multiplexing logic for the address, data and byte enable data paths for the PS and PM busses.

The PM and PS busses are described in detail in the SSA7785 ThunderBird Avenger™ Internal Busses section. Parti-

tioning of these PCI blocks are done in this manner to reduce block inter-connectivity and to provide an interface

between the three major sections of the PCI interface.

PCI Master Interface

The SSA7785 ThunderBird Avenger™ PCI master interface performs the memory read and write cycles initiated by the

DMA or Virtual Registers blocks. The major components of the PCI master interface are the master state machine, the

PM bus arbiter and the master control logic. Each of the functional blocks will be discussed in detail.

Device Cycle Types

Data

Width Comments

PCI Configuration

Registers

Config Read

Config Write

Any Follow PCI addressing rules, otherwise assert a target abort.

Note that configuration registers, no matter where they are,

are accessed by configuration cycles only. Note that the PLL

will only allow 8 bit configuration accesses, the Virtual Regis-

ters TBLBASE registers are 32 bit access only, and the

VRCFG is 16 bit access only.

Game Port I/O Read

I/O Write

8 Any other access will result in a target abort.

AC’97 Codec I/O Read

I/O Write

16 For PIO type accesses, only 16 bit I/O cycles are allowed,

other wise a target abort will result.

DMA Interface I/O R/W Any

Sound Blaster Regis-

ters

I/O Read

I/O Write

8 Any other access will result in a target abort.

Virtual Registers Mem Read Any Follow PCI addressing rules.

Host/DSP Interface I/O Read

I/O Write

8,16 Usually, only 16 bit accesses will be used to download and

access the DSP. Byte wide are also allowed for DSP config-

uration accesses. Word accesses must be on word bound-

aries.

MPU401 Registers I/O Read

I/O Write

8 Any other access will result in a target abort.

16650 UART I/O Read

I/O Write

8 Any other access will result in a target abort.