ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 60

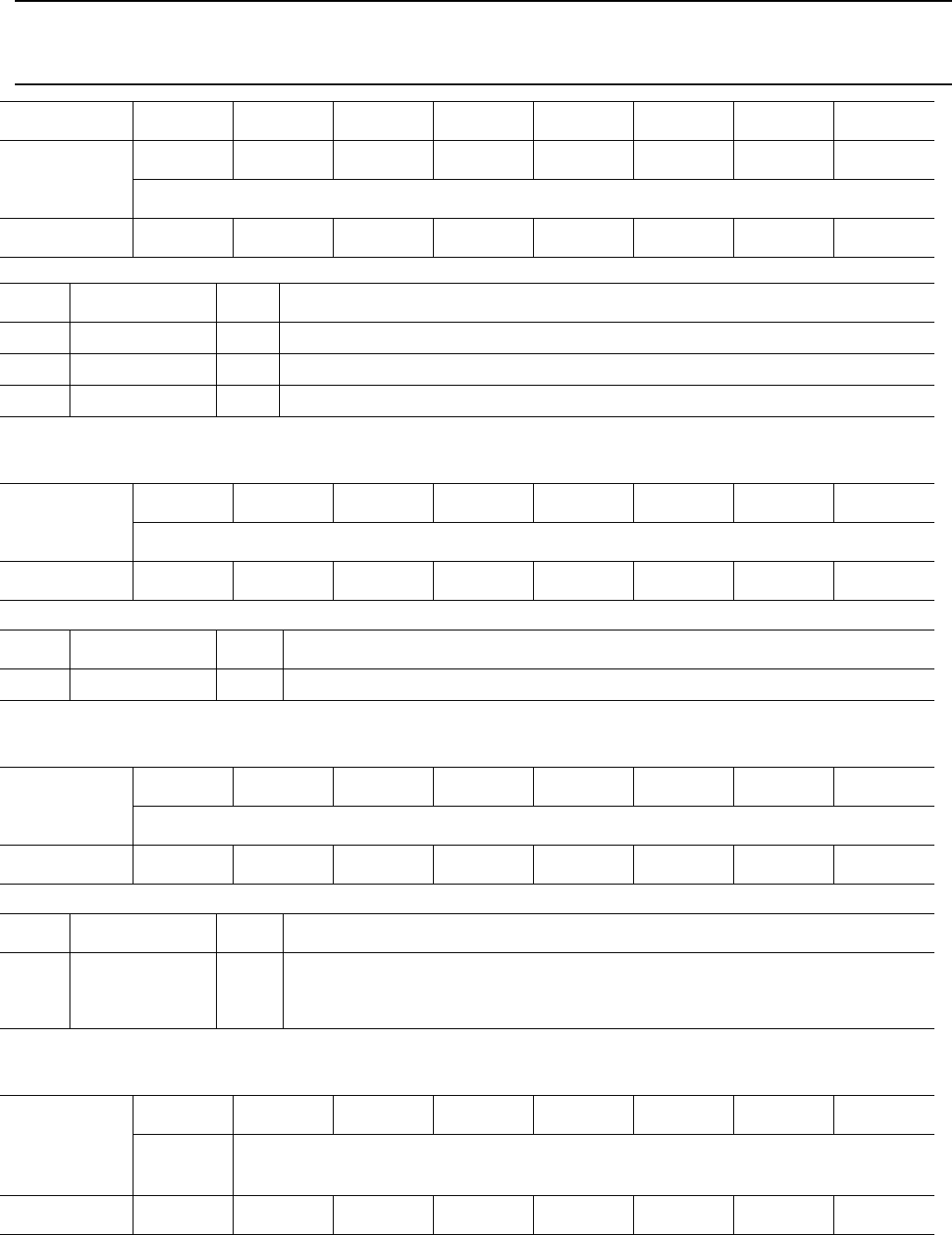

TABLE 58 CACHELINE Size Register - CACHELINE (RO)

TABLE 59 Master Latency Timer Register - LATIME (RW)

TABLE 60 Header Type Register - HEADER (RO)

D7 D6 D5 D4 D3 D2 D1 D0

PGM_IFACE[7:0]

POR Value

00000010

Bit Name R/W Function

23:16 BASE_CLASS RO The base class of 07h describes simple communication devices.

15:8 SUB_CLASS RO The sub class of 00h describes serial controllers.

7:0 PGM_IFACE RO The interface of 02h details a 16550 compatible serial controller.

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 0Ch

CACHELINE[7:0]

POR Value

00000000

Bit Name R/W Function

7:0 CACHELINE RO Reserved for cache line size indicator.

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 0Dh

LATIME[7:0]

POR Value

00000000

Bit Name R/W Function

7:0 LATIME RO The primary bus latency timer specifies the number of primary clocks that the

primary master may consume. It is set to zero since the 16650 UART is a tar-

get only.

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 0Eh

MULTI_

FN

HEADER[6:0]

POR Value

10000000

PCI CFG 2 D23 D22 D21 D20 D19 D18 D17 D16