ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 59

Note: An RC indicates that this bit can be reset to 0 by writing a 1. Writing a zero leaves this bit unchanged.

TABLE 56 Revision ID Register - REVISION (RO)

TABLE 57 Class Code Register - CLASS (RO)

11 ST_ABORT RC Signalled Target Abort: When set to 1, this bit indicates that the SSA7785

ThunderBird Avenger™, function 2 has signalled a target abort at least once

since this bit was last reset.

10:9 DEVSEL_TM

G

RO DEVSEL Timing: This field indicates the timing of the DEVSEL output (when

a PCI master is accessing a SSA7785 ThunderBird Avenger™ resource). It

always returns 01 (Bin).

00 = Fast

01 = Medium (Default Timing)

10 = Slow

8 S_PERR RO Signalled Parity Error: The SSA7785 ThunderBird Avenger™, function 2,

does not act as a bus master.

7 F_BK2BK RO Always returns 1 to indicate support of fast back to back cycles when the

SSA7785 ThunderBird Avenger™, function 2 is the target.

6 UDF RO User Definable Features. Always returns 0.

5 MHz66 RO 66 MHz Capable. Always returns 0.

4:0 R RO Reserved. These bits always return zero.

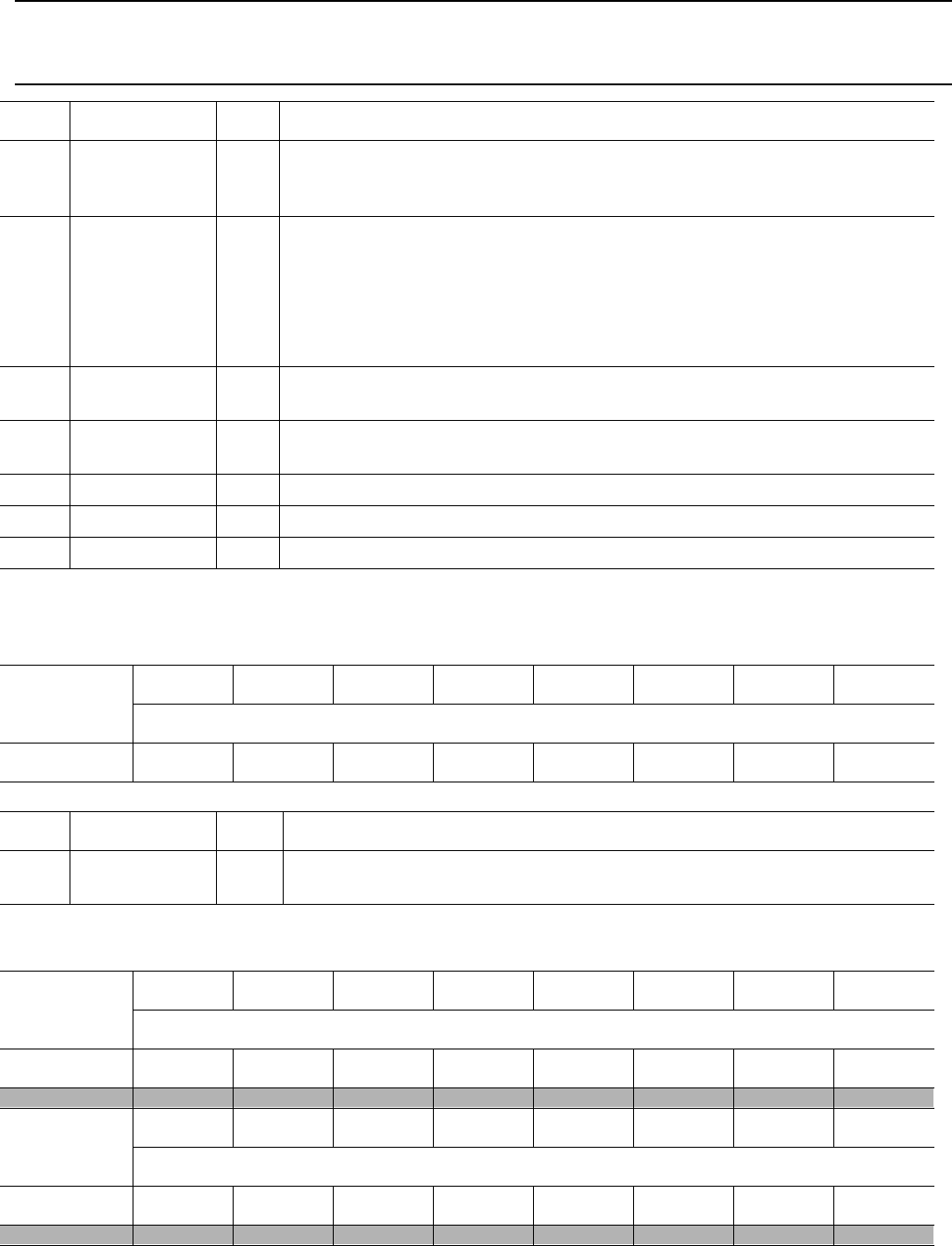

PCI CFG 2D7D6D5D4D3D2D1D0

Offset 08h

REVISION_ID[7:0]

POR Value

00000000

Bit Name R/W Function

7:0 REVISION_ID RO The current revision ID for the SSA7785 ThunderBird Avenger™, function 2

joystick..

PCI CFG 2 D23 D22 D21 D20 D19 D18 D17 D16

Offset 09h

BASE_CLASS[7:0]

POR Value

00000111

D15 D14 D13 D12 D11 D10 D9 D8

SUB_CLASS[7:0]

POR Value

00000000

Bit Name R/W Function