ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 57

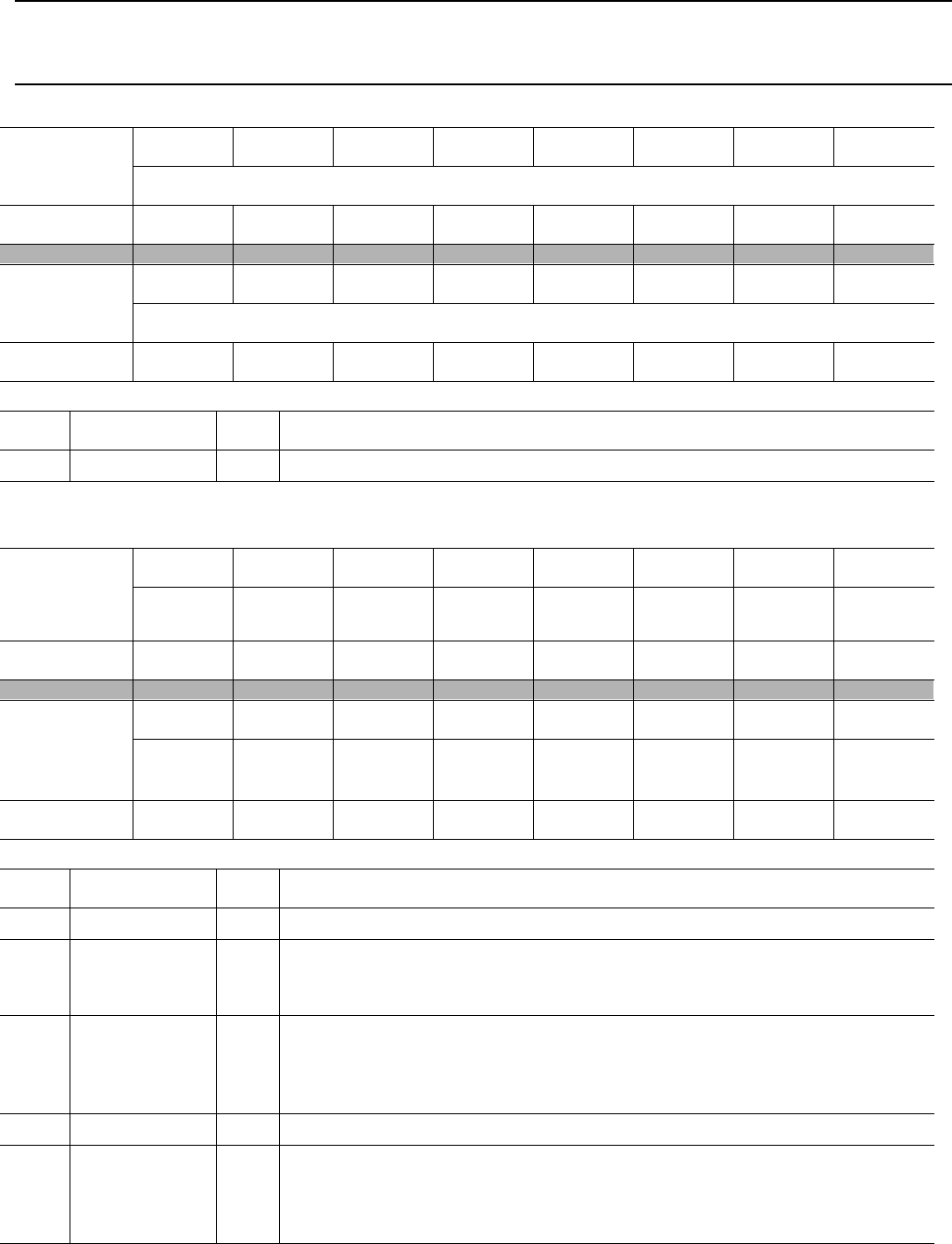

TABLE 53 Device ID Register - DEVICE_ID (RO)

TABLE 54 Command Register - COMMAND (RO/RW)

PCI CFG 2 D15 D14 D13 D12 D11 D10 D9 D8

Offset 02h

DEVICE_ID[15:8]

POR Value

00000011

D7 D6 D5 D4 D3 D2 D1 D0

DEVICE_ID[7:0]

POR Value

00000110

Bit Name R/W Function

15:0 DEVICE_ID RO The Device ID for the SSA7785 ThunderBird Avenger™, function 2 is 0306h.

PCI CFG 2 D15 D14 D13 D12 D11 D10 D9 D8

Offset 04h

RRRRRRFBACK_

ENB

SERR_R

ESP

POR Value

00000000

D7 D6 D5 D4 D3 D2 D1 D0

STEP-

PING

PERR_

RESP

SNOOP_

ENB

MEM_

INV_EN

SPEC_

CNTL

MAST_

CNTL

MEM_

CNTL

IO_

CNTL

POR Value

00000000

Bit Name R/W Function

15:10 R RO Reserved. These bits always return zero.

9 FBACK_ENB RO Fast Back-to-Back Enable: the SSA7785 ThunderBird Avenger™, function 2

does not support fast back to back master cycles therefore this bit always

returns a zero.

8 SERR_RESP RW System Error Response: When set to 1, the SSA7785 ThunderBird

Avenger™, function 2 responds to detected PCI bus address parity errors by

asserting SERR#. When 0, the SSA7785 ThunderBird Avenger™ ignores

these errors.

7 STEPPING RO Address / Data Stepping: Always returns 0.

6 PERR_RESP RW Parity Error Response: When set to 1, the SSA7785 ThunderBird Avenger™,

function 2 responds to detected PCI bus data parity errors by asserting

PERR#. When 0, the SSA7785 ThunderBird Avenger™ ignores PCI bus data

parity errors.