ThunderBird Avenger

TM

PCI Audio SAA7785

Accelerator

Philips Semiconductors Preliminary Specification

1999 Nov 12 58

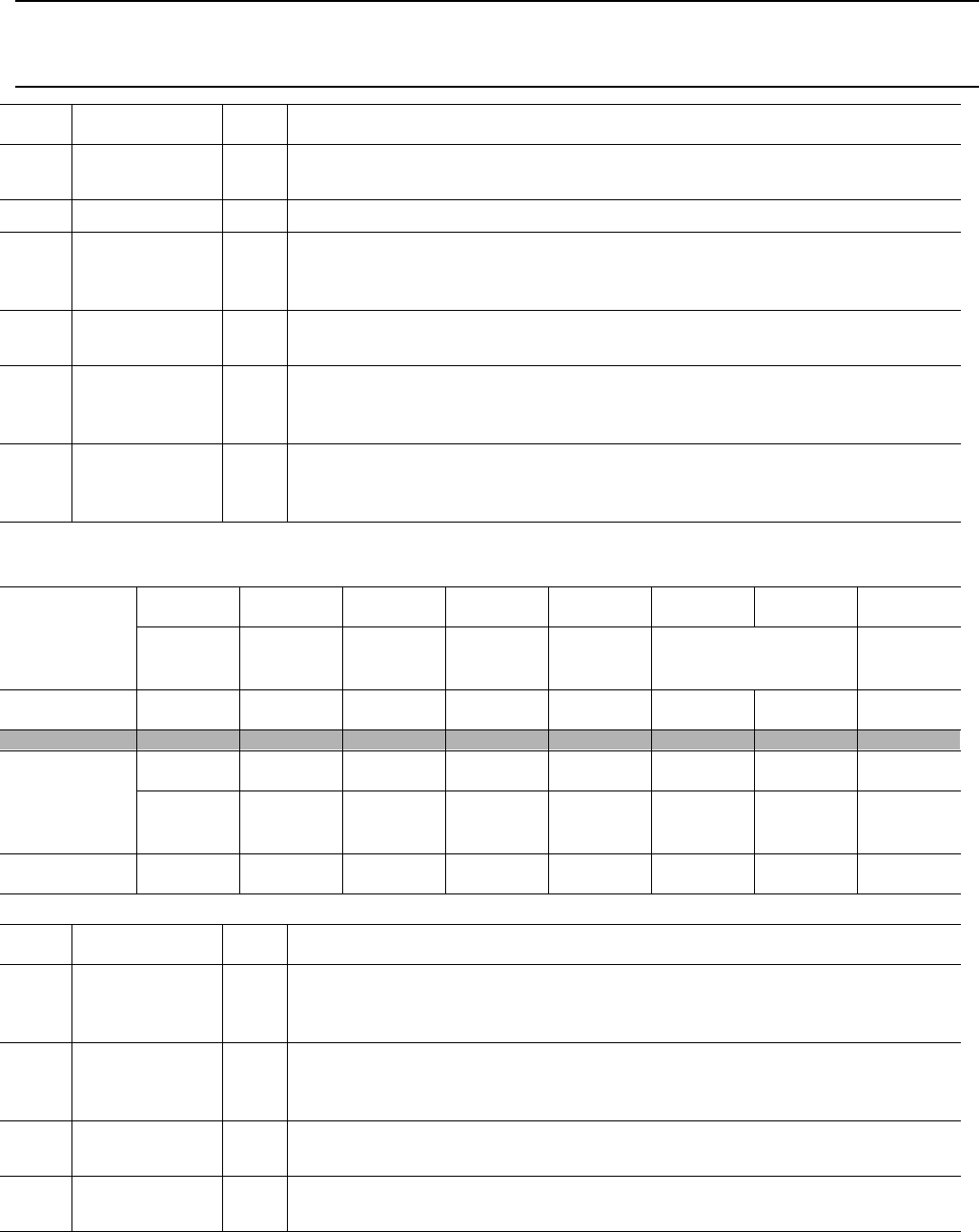

TABLE 55 Status Register - STATUS (RO/RW)

5 SNOOP_ENB RO VGA Snoop Enable. The SSA7785 ThunderBird Avenger™, function 2 does

not support VGA snoop enable, therefor this bit always returns a zero.

4 MEM_INV_EN RO Memory Write and Invalidate Enable: Always returns 0.

3 SPEC_CNTL RO Special Cycle Control: Controls the devices ability to respond to Special

Cycle Operations. A value of 0 causes the SSA7785 ThunderBird Avenger™,

function 2 to ignore all Special Cycles.

2 MAST_CNTL RO Master Control: The SSA7785 ThunderBird Avenger™, function 2 does not

have any master functions.

1 MEM_CNTL RO Memory Response Control: The SSA7785 ThunderBird Avenger™, function 2

does not support target memory cycles therefore this bit always returns a

zero.

0 IO_CNTL RW I/O Response Control: Controls the SSA7785 ThunderBird Avenger™, func-

tion 2’s response to I/O space. A value of 0 disables the device response. A

value of 1 allows the device to respond to I/O space accesses.

PCI CFG 2 D15 D14 D13 D12 D11 D10 D9 D8

Offset 06h

R_PERR S_SERR SM_

ABORT

RT_

ABORT

ST_

ABORT

DEVSEL_TMG S_PERR

POR Value

00000010

D7 D6 D5 D4 D3 D2 D1 D0

F_

BK2BK

UDFMHz66RRRRR

POR Value

10000000

Bit Name R/W Function

15 R_PERR RC Received Parity Error: When set to 1, this bit indicates that the SSA7785

ThunderBird Avenger™, function 2 has detected a PCI bus parity error at

least once since this bit was last reset.

14 S_SERR RC Signalled System Error: When set to 1, this bit indicates that the SSA7785

ThunderBird Avenger™, function 2 has reported a system error on the

SERR# signal at least once since this bit was last reset.

13 SM_ABORT RO Signalled Master Abort: The SSA7785 ThunderBird Avenger™, function 2,

does not act as a master.

12 RT_ABORT RO Received Target Abort: The SSA7785 ThunderBird Avenger™, function 2

does not act as a master.

Bit Name R/W Function