APPLICATION

2-60

4513/4514 Group User’s Manual

2.9 RAM back-up

Remarks

Set the port using the key-on wakeup function selected

with register K0 to “H” level before going into the RAM

back-up state because the port P0 shares the falling

edge detection circuit with port P1.

Select the return level (“L” level or “H” level) with the bit

2 of register I1 according to the external state before

going into the RAM back-up state.

Select the return level (“L” level or “H” level) with the bit

2 of register I2 according to the external state before

going into the RAM back-up state.

Return condition

Return by an external falling

edge input (“H”→“L”).

Return by an external “H” level

or “L” level input.

The EXF0 flag is not set.

Return by an external “H” level

or “L” level input.

The EXF1 flag is not set.

Table 2.9.2 Return source and return condition

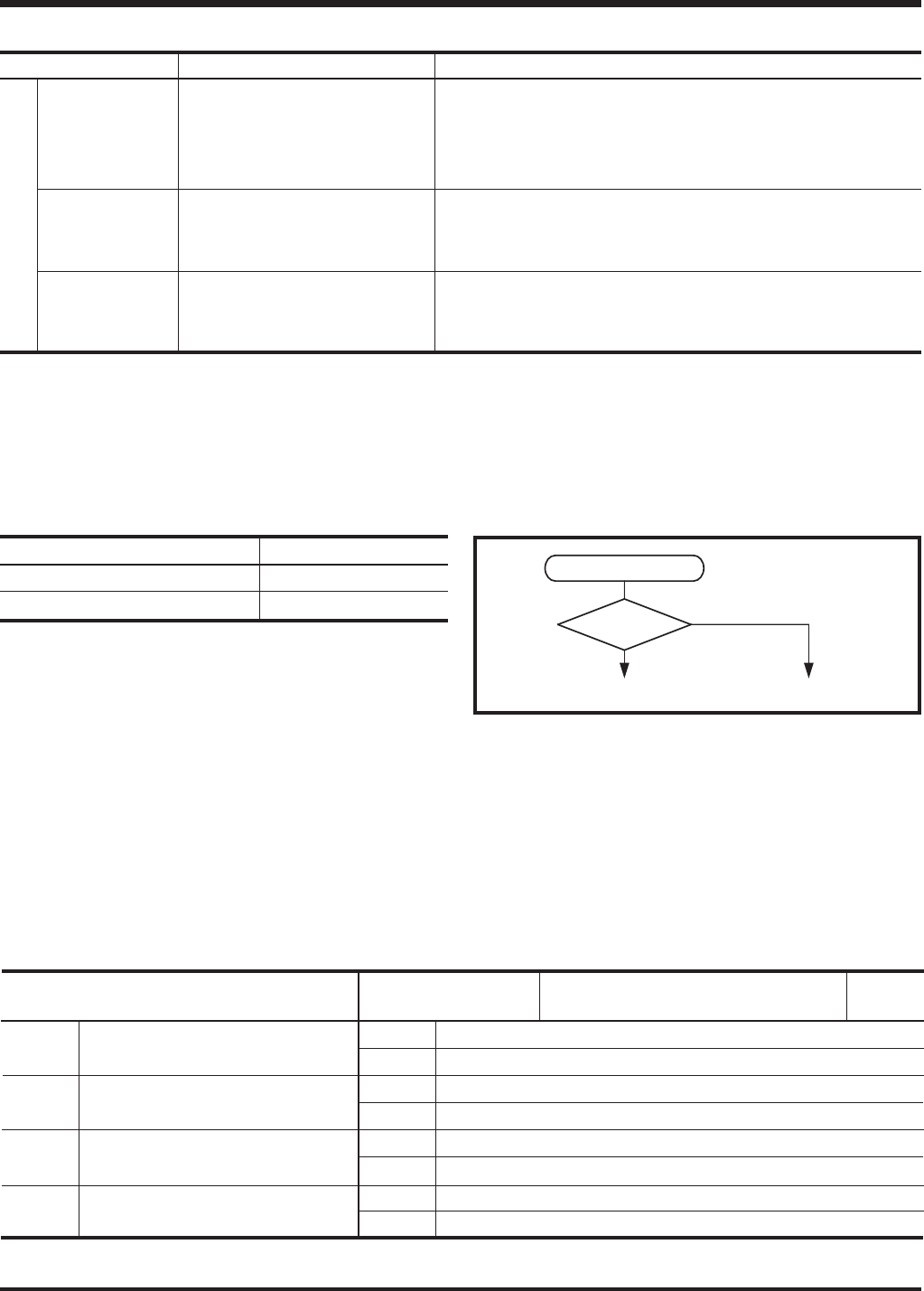

(2) Start condition identification

When system returns from both RAM back-up mode and reset, software is started from address 0

in page 0.

The start condition (warm start or cold start) can be identified by examining the state of the power

down flag (P) with the SNZP instruction.

Table 2.9.3 Start condition identification

Fig. 2.9.1 Start condition identified example

Return source

Ports P0, P1

Port P30/INT0

Port P31/INT1

External wakeup

signal

Return condition

External wakeup signal input

Reset

P flag

1

0

Software start

P = “1”

?

Yes

Warm start

Cold start

No

2.9.2 Related register

(1) Key-on wakeup control register K0

Key-on wakeup control register K0 controls key-on wakeup functions of ports P00–P03, P10–P13.

Set the contents of this register through register A with the TK0A instruction. The TAK0 instruction

can be used to transfer the contents of register K0 to register A.

Table 2.9.4 shows the key-on wakeup control register K0.

Table 2.9.4 Key-on wakeup control register K0

Key-on wakeup control register K0 at reset : 00002 at RAM back-up : state retained

R/W

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Key-on wakeup not used

Key-on wakeup used

Pins P12 and P13 key-on wakeup

control bit

Pins P10 and P11 key-on wakeup

control bit

Pins P02 and P03 key-on wakeup

control bit

Pins P00 and P01 key-on wakeup

control bit

0

1

0

1

0

1

0

1

K03

K02

K01

K00

Note: “R” represents read enabled, and “W” represents write enabled.