1-86

HARDWARE

4513/4514 Group User’s Manual

Selected pins

AIN0

AIN1

AIN2

AIN3

AIN4 (Not available for the 4513 Group)

AIN5 (Not available for the 4513 Group)

AIN6 (Not available for the 4513 Group)

AIN7 (Not available for the 4513 Group)

This bit has no function, but read/write is enabled.

Instruction clock signal divided by 8

Instruction clock signal divided by 4

Input ports P20, P21, P22 selected

Serial I/O ports SCK, SOUT, SIN/input ports P20, P21, P22 selected

External clock

Internal clock (instruction clock divided by 4 or 8)

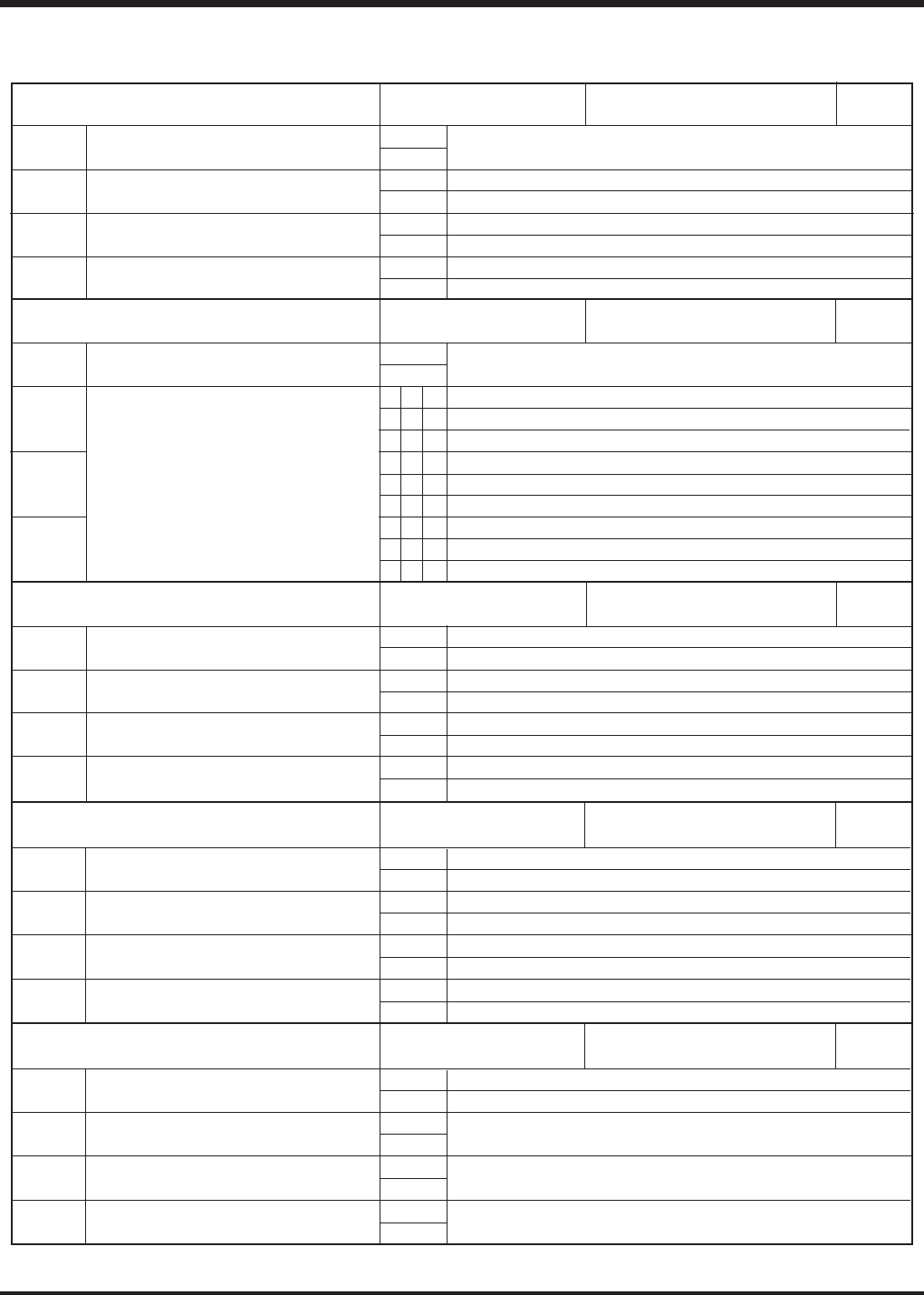

J13

J12

J11

J10

Serial I/O mode register J1

Not used

Serial I/O internal clock dividing ratio

selection bit

Serial I/O port selection bit

Serial I/O synchronous clock selection bit

at reset : 00002

at RAM back-up : state retained

0

1

0

1

0

1

0

1

R/W

Q13

Q12

Q11

Q10

A-D control register Q1

Note used

Analog input pin selection bits (Note 2)

at reset : 00002 at RAM back-up : state retained

0

1

Q12

0

0

0

0

1

1

1

1

Q11

0

0

1

1

0

0

1

1

This bit has no function, but read/write is enabled.

at reset : 00002

Q23

Q22

Q21

Q20

A-D control register Q2

A-D conversion mode

Comparator mode

P43, P42 (read/write enabled for the 4513 Group)

AIN7, AIN6/P43, P42(read/write enabled for the 4513 Group)

P41 (read/write enabled for the 4513 Group)

AIN5/P41 (read/write enabled for the 4513 Group)

P40 (read/write enabled for the 4513 Group)

AIN4/P40 (read/write enabled for the 4513 Group)

A-D operation mode selection bit

P43/AIN7 and P42/AIN6 pin function selec-

tion bit (Not used for the 4513 Group)

P41/AIN5 pin function selection bit

(Not used for the 4513 Group)

P40/AIN4 pin function selection bit

(Not used for the 4513 Group)

at RAM back-up : state retained

0

1

0

1

0

1

0

1

Notes 1: “R” represents read enabled, “W” represents write enabled.

2: Select A

IN4–AIN7 with register Q1 after setting register Q2.

3: Bits 0 and 1 of register Q3 can be only read.

Q10

0

1

0

1

0

1

0

1

R/W

R/W

MR3

MR2

MR1

MR0

Clock control register MR

f(XIN) (high-speed mode)

f(XIN)/2 (middle-speed mode)

This bit has no function, but read/write is enabled.

This bit has no function, but read/write is enabled.

This bit has no function, but read/write is enabled.

System clock selection bit

Not used

Not used

Not used

at reset : 10002 at RAM back-up : 10002

0

1

0

1

0

1

0

1

R/W

Q33

Q32

Q31

Q30

Comparator control register Q3 (Note 3) at reset : 00002 at RAM back-up : state retained

0

1

0

1

0

1

0

1

R/W

Voltage comparator (CMP1) invalid

Voltage comparator (CMP1) valid

Voltage comparator (CMP0) invalid

Voltage comparator (CMP0) valid

CMP1- > CMP1+

CMP1- < CMP1+

CMP0- > CMP0+

CMP0- < CMP0+

Voltage comparator (CMP1) control bit

Voltage comparator (CMP0) control bit

CMP1 comparison result store bit

CMP0 comparison reslut store bit

CONTROL REGISTERS