4513/4514 Group User’s Manual

HARDWARE

1-15

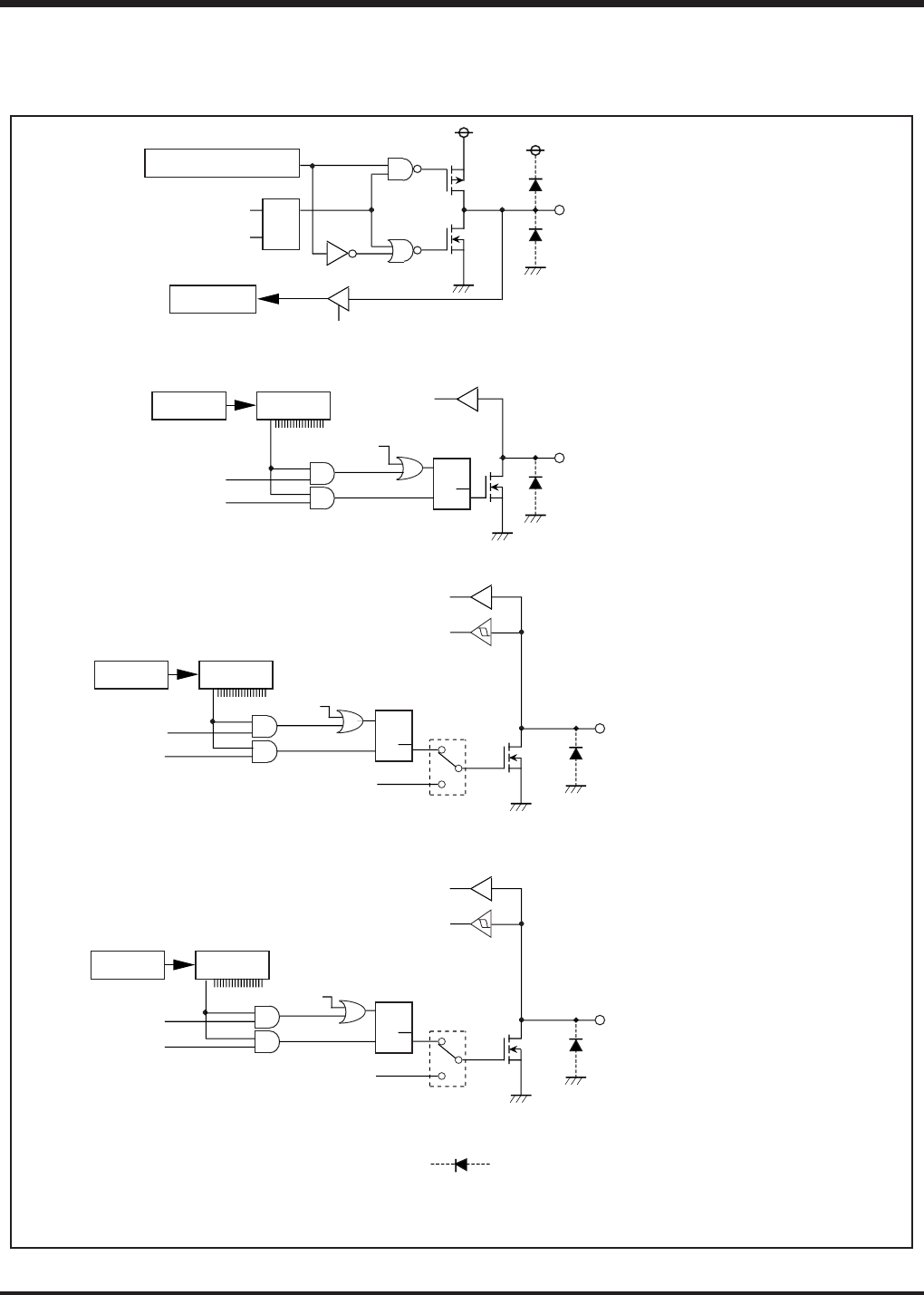

PORT BLOCK DIAGRAMS (continued)

PIN DESCRIPTION

P5

0

–P5

3

D

T

Q

OP5A instruction

Ai

Register A

IAP5 instruction

D

0

–D

5

SD instruction

S

R

Q

Decoder

Skip decision

(SZD instruction)

Register Y

RD instruction

D

6

/CNTR0

S

R

Q

Skip decision

(SZD instruction)

SD instruction

DecoderRegister Y

RD instruction

0

1

W6

0

Timer 1 underflow signal divided by 2 or

signal of AND operation between

timer 1 underflow signal divided by 2 and

timer 2 underflow signal divided by 2

Clock input for timer 2 event count

D

7

/CNTR1

S

R

Q

0

1

W6

2

Direction register FR0i

Skip decision

(SZD instruction)

SD instruction

DecoderRegister Y

RD instruction

Clock input for timer 4 event count

This symbol represents a parasitic diode on the port.

• Applied potential to ports D

0

–D

7

must be 12 V.

• i represents 0, 1, 2, or 3.

• The 4513 Group does not have port P5.

•

CLD instruction

Timer 3 underflow signal divided by 2 or

signal of AND operation between

timer 3 underflow signal divided by 2 and

timer 4 underflow signal divided by 2

CLD instruction

CLD instruction