4513/4514 Group User’s Manual

HARDWARE

1-35

FUNCTION BLOCK OPERATIONS

WATCHDOG TIMER

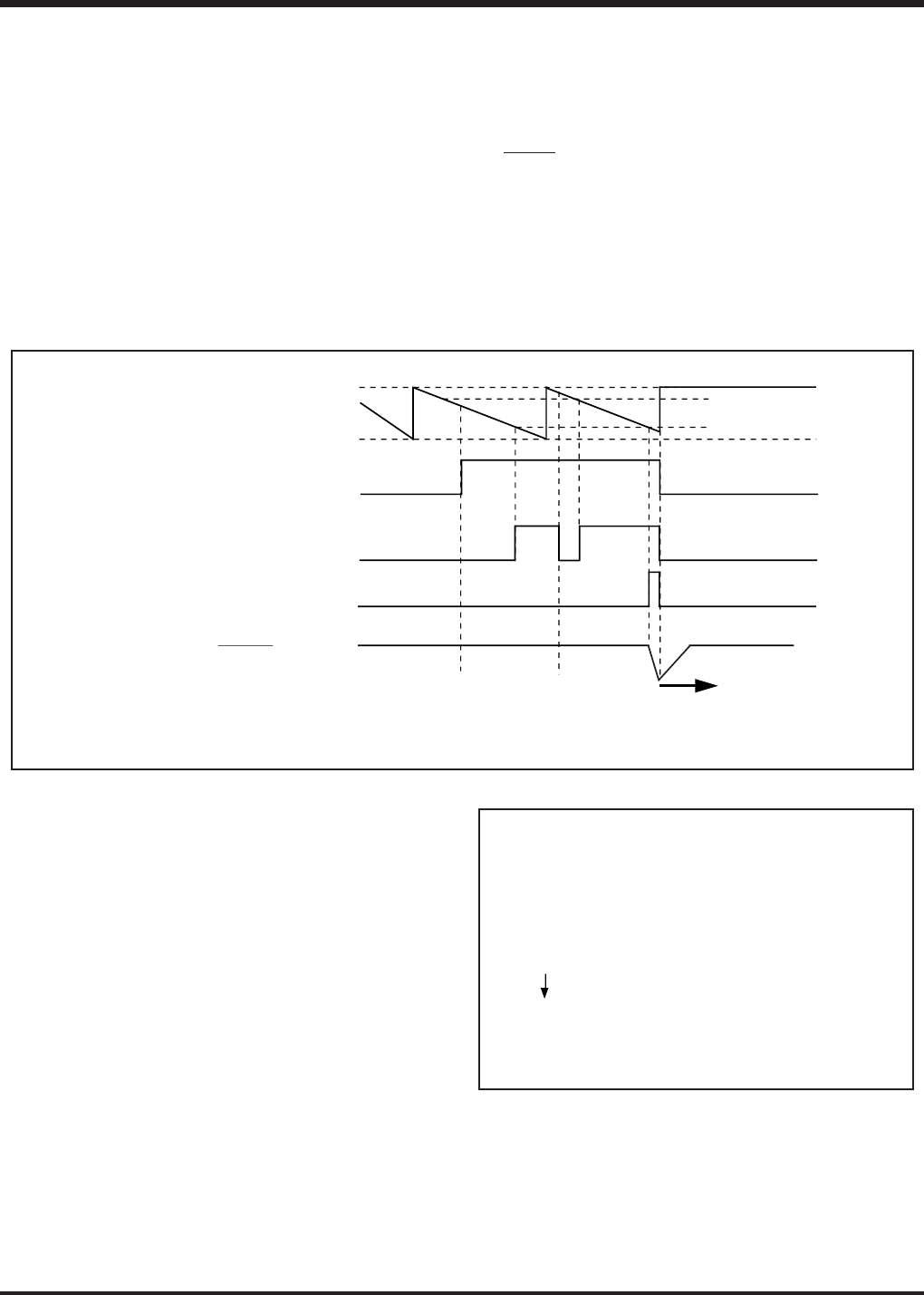

Watchdog timer provides a method to reset the system when a pro-

gram runs wild. Watchdog timer consists of a 16-bit timer (WDT),

watchdog timer enable flag (WEF), and watchdog timer flags

(WDF1, WDF2).

The timer WDT downcounts the instruction clocks as the count

source. The underflow signal is generated when the count value

reaches “000016.” This underflow signal can be used as the timer 2

count source.

When the WRST instruction is executed after system is released

from reset, the WEF flag is set to “1”. At this time, the watchdog

timer starts operating.

When the count value of timer WDT reaches “BFFF16” or “3FFF16,”

the WDF1 flag is set to “1.” If the WRST instruction is never ex-

ecuted while timer WDT counts 32767, WDF2 flag is set to “1,” and

the RESET pin outputs “L” level to reset the microcomputer. Ex-

ecute the WRST instruction at each period of 32766 machine cycle

or less by software when using watchdog timer to keep the micro-

computer operating normally.

To prevent the WDT stopping in the event of misoperation, WEF

flag is designed not to initialize once the WRST instruction has

been executed. Note also that, if the WRST instruction is never ex-

ecuted, the watchdog timer does not start.

Fig. 20 Watchdog timer function

The contents of WEF, WDF1 and WDF2 flags and timer WDT are

initialized at the RAM back-up mode.

If WDF2 flag is set to “1” at the same time that the microcomputer

enters the RAM back-up state, system reset may be performed.

When using the watchdog timer and the RAM back-up mode, ini-

tialize the WDF1 flag with the WRST instruction just before the

microcomputer enters the RAM back-up state (refer to Figure 21)

Fig. 21 Program example to enter the RAM back-up mode

when using the watchdog timer

WRST ; WDF1 flag reset

•

•

•

POF

EPOF ; POF instruction enabled

(RAM back-up state)

•

•

•

Oscillation

stop

FFFF16

0000 16

3FFF16

BFFF16

The value of timer (WDT)

WDF1 flag

WDF2 flag

WRST

instruction

executed

RESET pin output

System reset

WRST

instruction

executed

WEF flag