M/3

r

>00

36

37

38

39

40

Priority

Signal

Name

M32

FS

DSP2

CAS

2

Vcc

IN

OUT

OUT

OUT

IN

Clock

input

32MHz,

200

raster

Graphic

DRAM

address

multiplexer

signal

(High

order

8

bits

I ADS ADI 5]

/low

3'der

S hi"

|ADO AD7] select signal

)

Display

timing

signal

(In the CSP 2, the

signal

BLINK

from

GDC2

is

delayed

by 2

collor

intervals

to

create

this signal

)

Graphic

D RAM CAS

(COLUMN

ADDRESS

SELECT)

signal

(Line

address

selection)

+

5V

supply

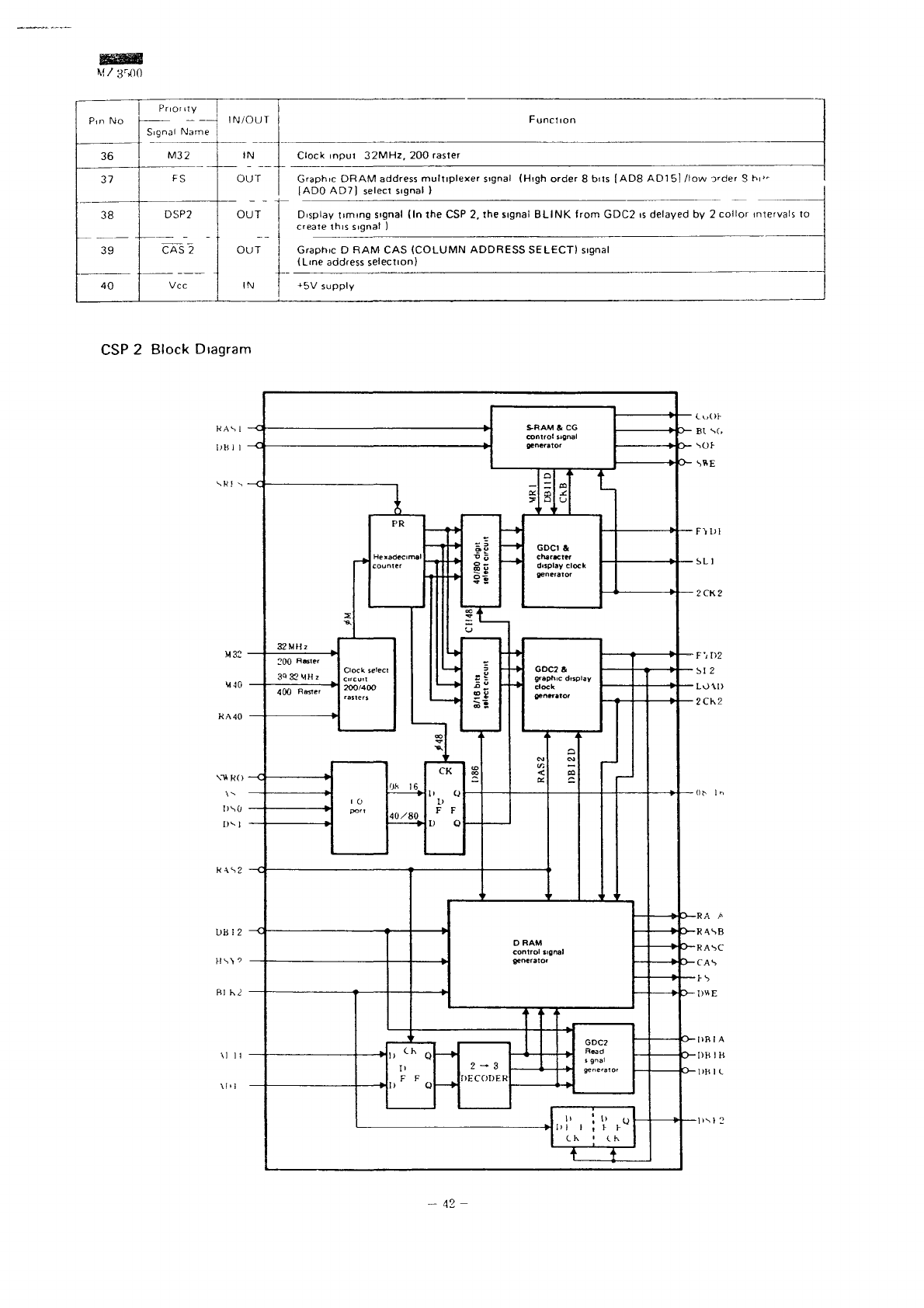

CSP

2

Block Diagram

VWRO

—

C

KAS2

—

C

Ubl 2

—

C

r*

-a.

32MHz

Jl

PR

Hexadecimal

counter

200

Raster

Clock

select

3«32MHz

^

ClfCU1

,

*M

n~, *

^00/41

4U(J HasTer

rasters

to

1

O

L>

•

Oh

16

40/80

,

c

F

™

O

D

£

5

8/1

6

bill

0 t

T

ft.

CK

Q

I)

F

F

O

5

select

circuit

S-RAM

& CG

control

signal

generator

C

i i

i ' '

:

co

3

6

GDC1

&

character

L

display

clock

generator

GOC2&

graphic

display

clock

generator

Cfi

DBI2D

^

F

'

DRAM

control

signal

generator

K

n

Q

2

— 3

)ECODER

' '

' •

GDC2

Read

ignal

generator

n

L}

h

P°

\ C K

t f

^—

Bl SC,

D-

SOf

O- SHE

O—HB

1 A

-

42

-