MZ

3500

•

Command flag:

"0"

when

succeedeing

8

bits

are a key

data.

"1"

when

it is a

command

or a

graphic control

data.

•

Data: Positive logic (negative logic

on the

cable)

•

Parity:

Odd

parity

up to 27 bit

from

the

correction flag.

2)

Interfacing

signals

CPU

level

•

D(K):

Output

data from

the

keyboard.

Positive

logic

•

ST(K): D(K) strobe signal. Also

use for

Active

H

interrupt

to the

CPU.

•

ACK(C): Acknowledge

signal

form

the

Active

H

CPU.

Also

use for the

data

transfer

interrupt

disable

signal.

•

D(C):

Output

data

from

the

CPU. Positive

logic

•

ST(C):

D(C)

strobe signal. Also

use for

Active

L

interrupt

to the

keyboard side.

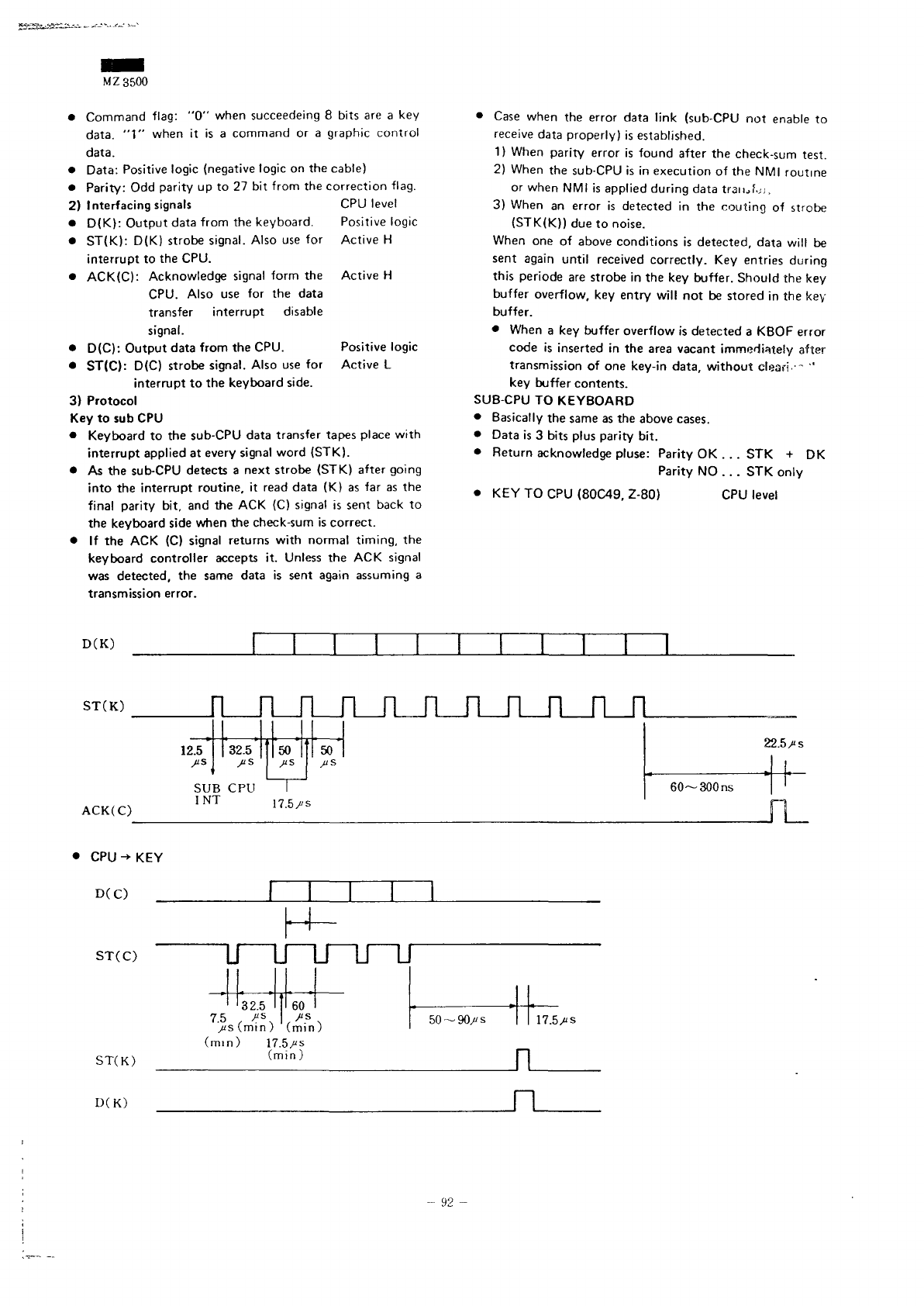

3)

Protocol

Key

to sub CPU

•

Keyboard

to the

sub-CPU data transfer tapes place

with

interrupt

applied

at

every

signal

word

(STK).

• As the

sub-CPU detects

a

next strobe (STK) after going

into

the

interrupt

routine,

it

read data

(K) as far as the

final

parity

bit,

and the ACK (C)

signal

is

sent back

to

the

keyboard side when

the

check-sum

is

correct.

• If the ACK (C)

signal returns

with

normal

timing,

the

keyboard

controller

accepts

it.

Unless

the ACK

signal

was

detected,

the

same

data

is

sent again assuming

a

transmission

error.

•

Case

when

the

error data

link

(sub-CPU

not

enable

to

receive

data

properly)

is

established.

1)

When

parity

error

is

found

after

the

check-sum test.

2)

When

the

sub-CPU

is in

execution

of the NMI

routine

or

when

NMI is

applied

during

data

tranJ.jj,

3)

When

an

error

is

detected

in the

couting

of

strobe

(STK(K))

due to

noise.

When

one of

above

conditions

is

detected, data

will

be

sent

again

until

received

correctly.

Key

entries

during

this

periode

are

strobe

in the key

buffer.

Should

the key

buffer

overflow,

key

entry

will

not be

stored

in the key

buffer.

•

When

a key

buffer

overflow

is

detected

a

KBOF error

code

is

inserted

in the

area

vacant

immediately

after

transmission

of one

key-in data,

without

clean

'~ "

key

buffer

contents.

SUB

CPU TO

KEYBOARD

•

Basically

the

same

as the

above

cases.

•

Data

is 3

bits

plus

parity

bit.

•

Return acknowledge pluse:

Parity

OK . .. STK + DK

Parity

NO ... STK

only

• KEY TO

CPU

(80C49,

Z-80)

CPU

level

D(K)

ST(K)

n__TL_n

12.5

32.5

50

50

ACK(C)

SUB CPU I

INT

17.5

,«s

22.5/-s

60~

300ns

CPU ->• KEY

D(C)

ST(C)

~ir~Ln_rrr~Lr

.

132.5

1

60

ST(K)

D(K)

7.5 *s AS

/<s

(mm)

(mm)

(mm)

17.5ys

(min)

50-90^5

Ji

n