M 7.

3500

Operational

description

(1)

Upon

reset

after

power

on, the

main

CPU

loads

the

contents

of the

initial

program

loader

(IPL)

into

RAM

starting

at

address

4000H,

during which time

reset

is

applied

to the

sub-CPU.

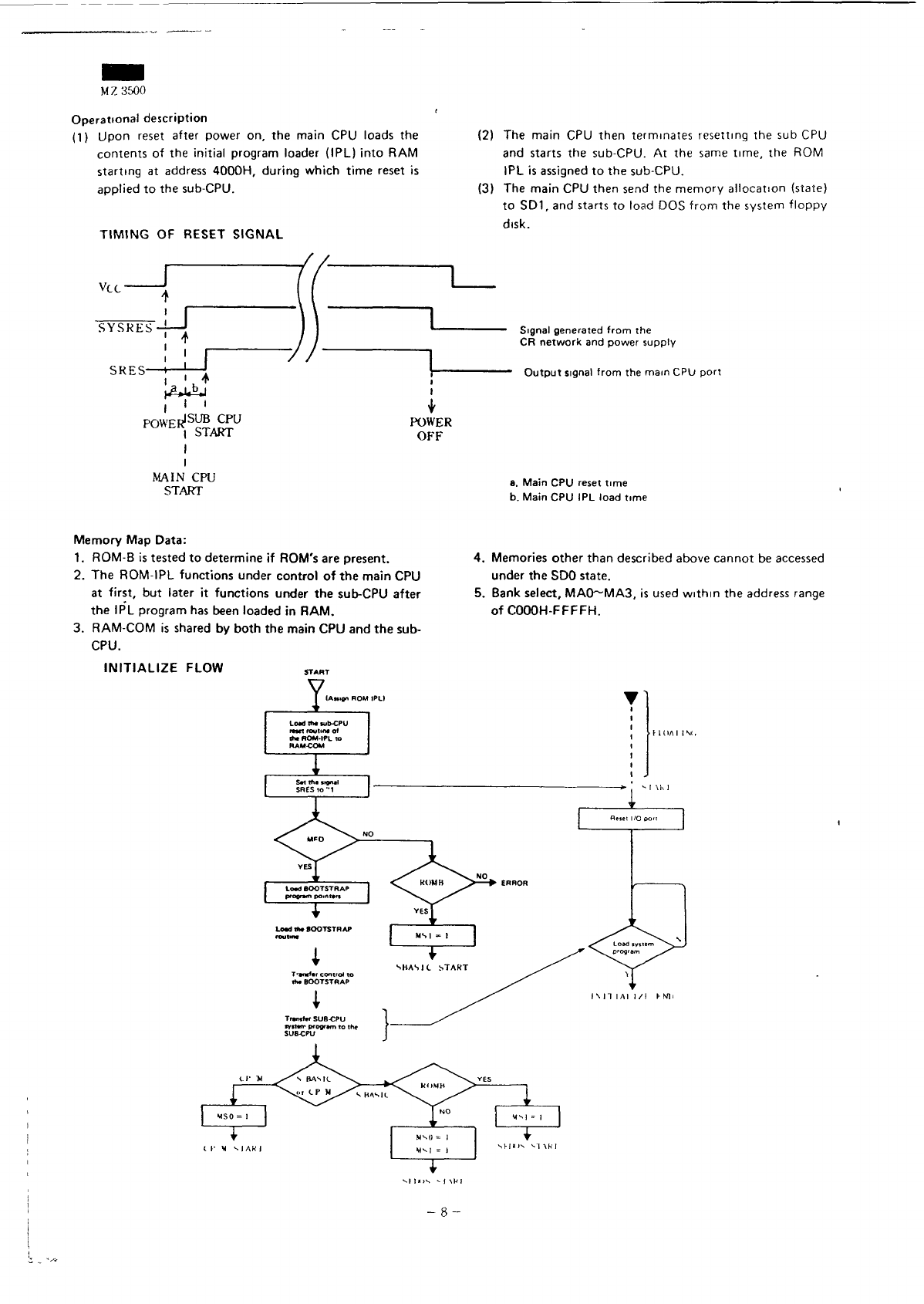

TIMING

OF

RESET

SIGNAL

Vtc-

SYSKES-

SKES-

pr)WF

jJSUB

CPU

PO

*

E

^

START

POWER

OFF

(2)

The

main

CPU

then

terminates

resetting

the sub CPU

and

starts

the

sub-CPU.

At the

same

time,

the ROM

IPL is

assigned

to the

sub-CPU.

(3)

The

main

CPU

then

send

the

memory

allocation

(state)

to

SD1,

and

starts

to

load

DOS

from

the

system

floppy

disk.

Signal

generated

from

the

CR

network

and

power supply

Output

signal

from

the

main

CPU

port

MAIN

CPU

START

a.

Main

CPU

reset

time

b.

Main

CPU IPL

load time

Memory

Map

Data:

1.

ROM-B

is

tested

to

determine

if

ROM's

are

present.

2. The

ROM-IPL functions under

control

of the

main

CPU

at

first,

but

later

it

functions under

the

sub-CPU after

the IPL

program

has

been

loaded

in

RAM.

3.

RAM-COM

is

shared

by

both

the

main

CPU and the

sub-

CPU.

INITIALIZE

FLOW

«T

ABT

4.

Memories

other

than

described

above

cannot

be

accessed

under

the SDO

state.

5.

Bank

select, MAO~MA3,

is

used

within

the

address

range

ofCOOOH-FFFFH.