M

2

3500

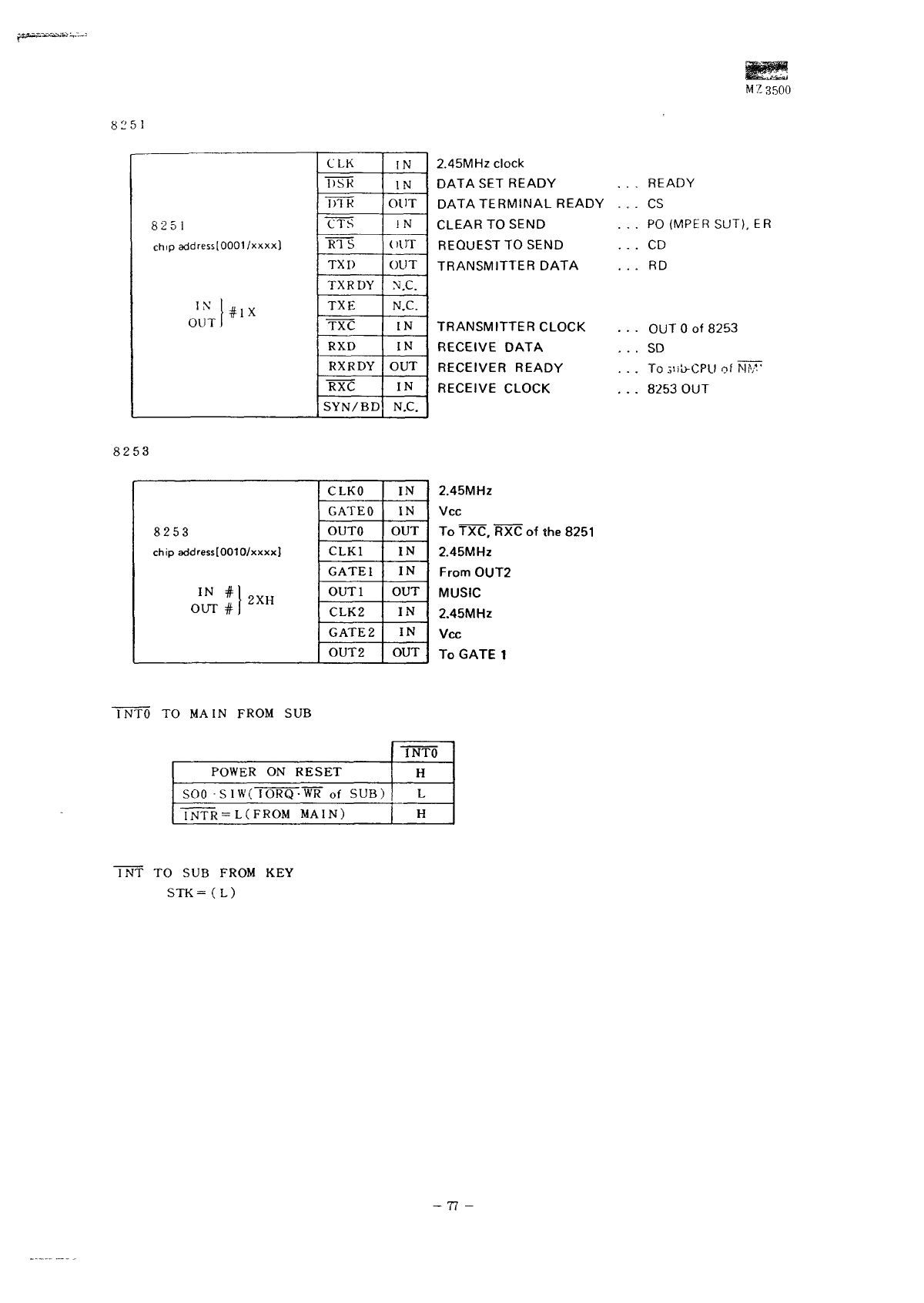

8251

8251

chip

address[0001/xxxx]

IN

Uix

OUT)

CLK

DSK

DTK

CTS

Rl

S

TXD

TXRDY

TXE

TXC

RXD

RXRDY

"RXC

SYN/BD

IN

IN

OUT

1

N

OUT

OUT

N.C.

N.C.

IN

IN

OUT

IN

N.C.

2.45MHz

clock

DATA

SET

READY

DATA TERMINAL READY

CLEAR

TO

SEND

REQUEST

TO

SEND

TRANSMITTER

DATA

TRANSMITTER

CLOCK

RECEIVE

DATA

RECEIVER

READY

RECEIVE

CLOCK

READY

CS

PO

(MPER

SUT),

ER

CD

RD

OUT

0 of

8253

SD

To

3iil>CPU

of

8253

OUT

8253

8253

chip

address[0010/xxxx]

IN

#UxH

OUT#|

2XH

CLKO

GATED

OUTO

CLK1

GATE1

OUT1

CLK2

GATE

2

OUT 2

IN

IN

OUT

IN

IN

OUT

IN

IN

OUT

2.45MHz

Vcc

To

TXC,

RXC of the

8251

2.45MHz

From OUT2

MUSIC

2.45MHz

Vcc

To

GATE

1

INTO

TO

MAIN

FROM

SUB

POWER

ON

RESET

SOO

-SIW(

IORQ-WR

of

SUB)

fNTR=L(FROM

MAIN)

INTO

H

L

H

INT

TO SUB

FROM

KEY

STK=

(L)

-

77

-