AMD

P R E L I M I N A R Y

134

Am79C930

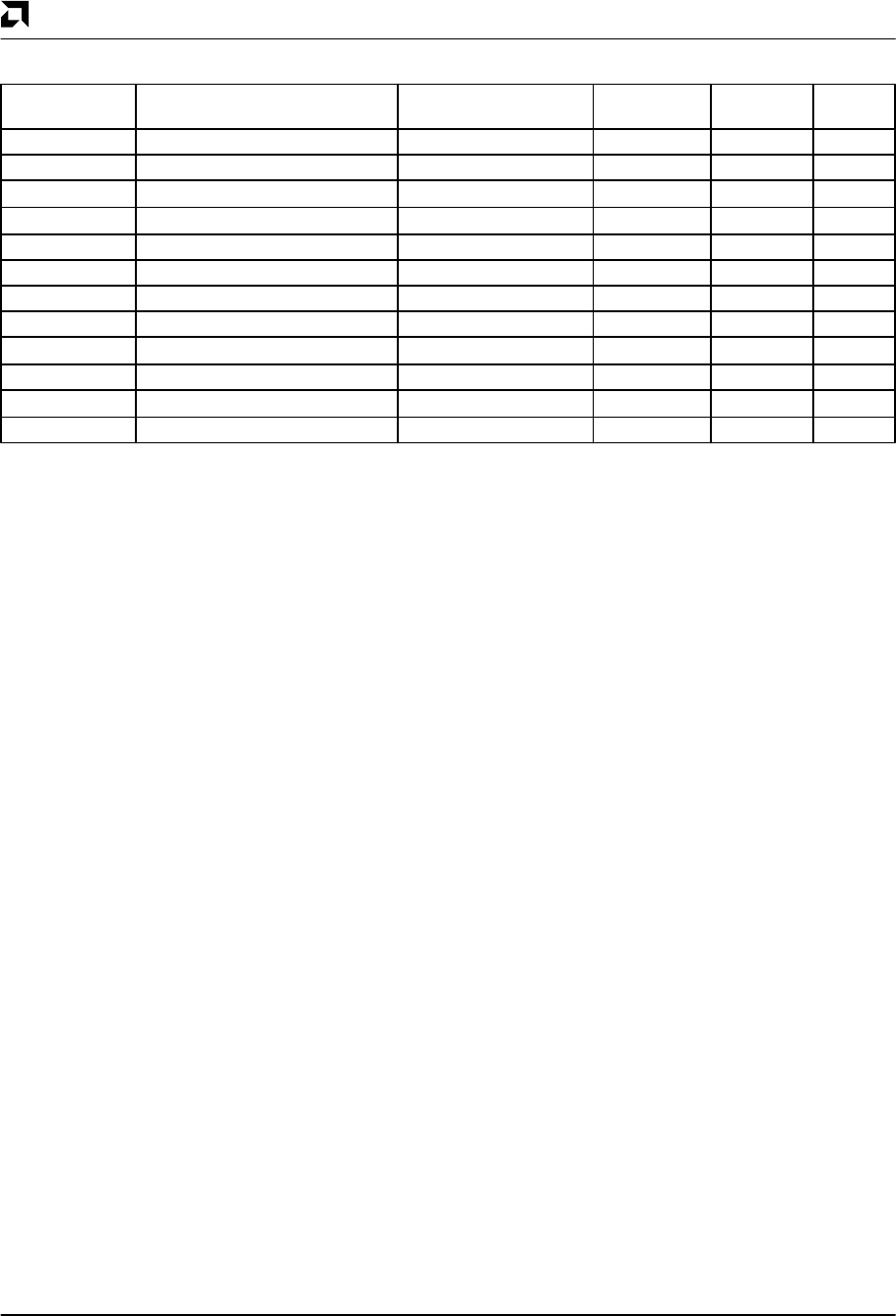

PCMCIA I/O WRITE ACCESS

Parameter

Symbol Parameter Description Test Conditions Min Max Unit

tAVIWL Address setup to IOWR ↓ 70 ns

tIWHAX Address hold from IOWR ↑ 20 ns

tRGLIWL REG setup to IOWR ↓ 5ns

tIWHRGH REG hold from IOWR ↑ 0ns

tELIWL CE setup to IOWR ↓ 5ns

tIWHEH CE hold from IOWR ↑ 20 ns

tIWLIWH IOWR width 165 ns

tIWLWTL WAIT ↓ delay from IOWR ↓ 35 ns

tWTLWTH WAIT width Notes 1, 2 53 X TCLKIN ns

tWTHIWH IOWR ↑ from WAIT ↑ 0ns

tDVIWL Data setup to IOWR ↓ 60 ns

tIWHDX Data hold from IOWR ↑ 30 ns

Notes:

1. The max value for this parameter assumes the following worst case situation:

Value Worst Case

0 FLASH and SRAM wait states set at “3.”

1 Host performs PCMCIA WRITE cycle at same time that Am79C930 embedded 80188 controller begins

instruction fetch cycle to FLASH memory.

2 PCMCIA WRITE cycle is posted internal to Am79C930 device, pending the completion of the embedded 80188

controller access.

3 Host performs PCMCIA READ cycle immediately following completion of PCMCIA WRITE cycle.

4 After completion of first embedded 80188 access to FLASH, posted PCMCIA WRITE executes to SRAM;

PCMCIISA READ stycle is being held in wait state.

5 After completion of posted PCMCIA WRITE cycle, new embedded 80188 access to FLASH begins.

6 After completion of second embedded 80188 access to FLASH, PCMCIA READ cycle is allowed to proceed onto

memory bus to SRAM; host is still held in wait state.

7 At SRAM READ cycle completion, data is delivered to PCMCIA bus and wait state is exited.

2. Parameter is not included in production test.