P R E L I M I N A R Y

AMD

41Am79C930

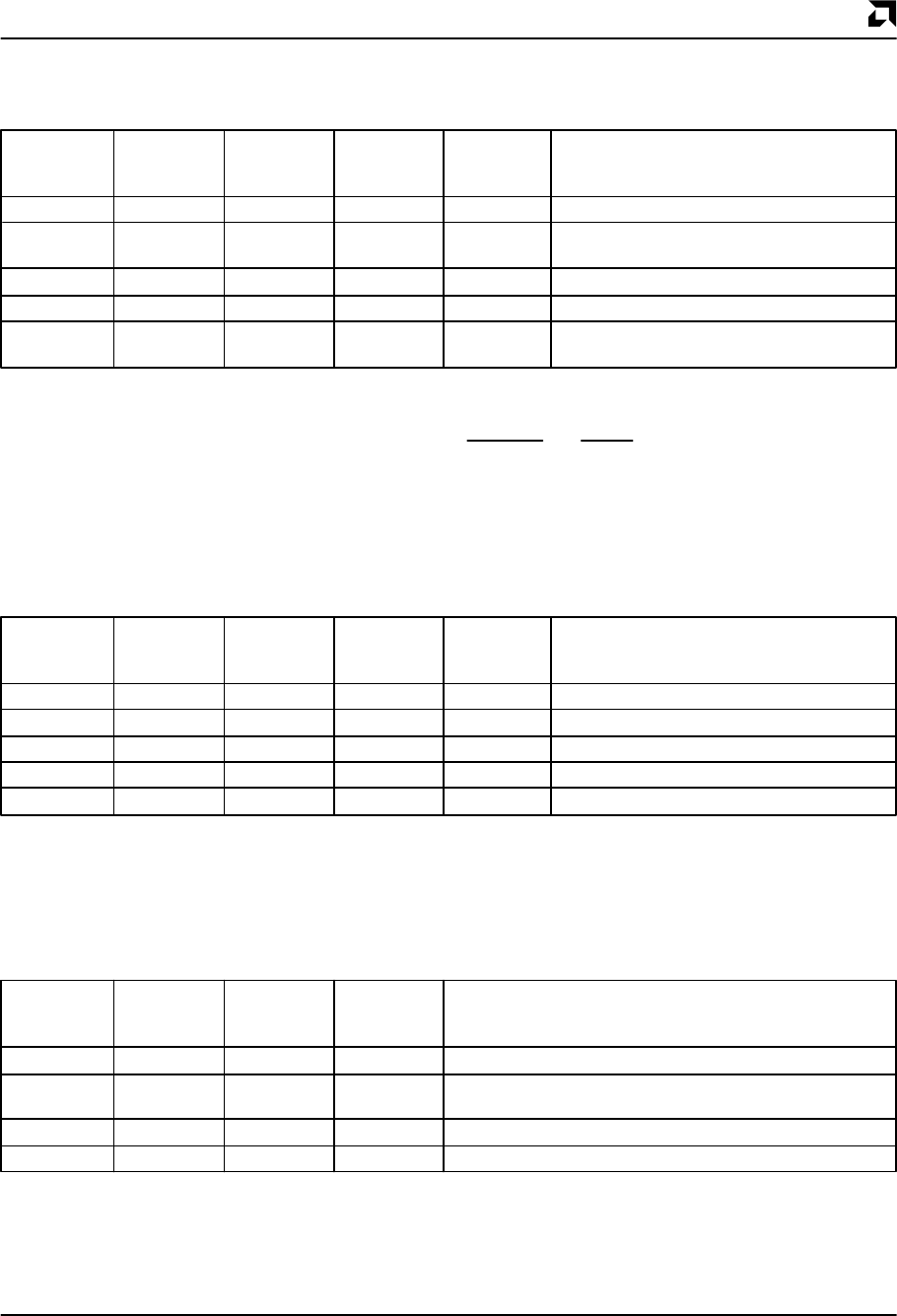

some functionality is only available in PCMCIA mode.

Pin functionality is programmed according to the follow-

ing table:

Note that a read of the ANTSLTD bit (TCR7[1]) will al-

ways give the current ANTSLT/LA23 pin value without

inversion, regardless of pin configuration setting.

ANTSLT/ ANTSLT/

PCMCIA ANTSEN ANSLTLFN ANTSLTLEN LA23 Pin LA23 Pin

Pin Value TIR26[3] TCR30[7] TCR15[7] Direction Value

0 X X X I NA (LA23 input function)

100XOANTSLT (from internal antenna)

(diversity circuit)

1X10I NA

1 X 1 1 O TCR7[1]

110XOTIR26[4] (write)

TIR26[5] (read)

Pin 142: TXCMD/LA21

The TXCMD/LA21 pin may be configured to operate as

input or output and may be configured to drive a trans-

ceiver control reference signal using one of two timing

sources plus input from the TXCMD bit of TIR11

(TIR11[0]). Note that some functionality is only available

in PCMCIA mode.

Pin functionality is programmed according to the

following table.

Transmit state machine generated signals T1, T2, T3,

TXP

_

ON

and

O_TX

have the timing indicated in the

diagram in section

Am79C930-Based TX Power

Ramp Control.

Note that a read of the TXCMDT bit (TCR7[2]) will al-

ways give the current TXCMD/LA21 pin value without

inversion, regardless of pin configuration setting.

TXCMD/ TXCMD/

PCMCIA RCEN TXCMFN TXCMEN LA21 Pin LA21 Pin

Pin Value TIR11[3] TCR30[5] TCR15[5] Direction Value

0 X X X I NA (LA21 input function)

1 0 X X O O_TX

1 1 0 X O TIR11[0] + T1

1110I NA

1 1 1 1 O TCR7[2]

Pin 143: TXDATA/LA20

The TXDATA/LA20 pin may be configured to operate as

input or output and may be configured to drive inverted

transmit data. Note that some functionality is only

available in PCMCIA mode. Pin functionality is pro-

grammed according to the following table:

The TXDATA signal is the inverse of the TXDATA signal

which is the TX data drawn from the TX FIFO using the

internal TX state machine control.

Note that a read of the TXDATALD bit (TCR7[0]) will al-

ways give the current TXDATA/LA20 pin value without

inversion, regardless of pin configuration setting.

TXDATA/ TXDATA/

PCMCIA TXDLFN TXDLEN LA20 Pin LA20 Pin

Pin Value TCR30[6] TCR15[6] Direction Value

0 X X I NA (LA20 input function)

10XOTXDATA (from internal TX FIFO

using internal TX state machine timing)

110INA

1 1 1 O TCR7[0]

Pin 144: LLOCKE/SA15

The LLOCKE/SA15 pin may be configured to operate as

input or output. Note that some functionality is only avail-

able in PCMCIA mode. Pin functionality is programmed

according to the following table:

Note that a read of the LLOCKE bit (TIR11[4]) will al-

ways give the current LLOCKE/SA15 pin value without

inversion, regardless of pin configuration setting.