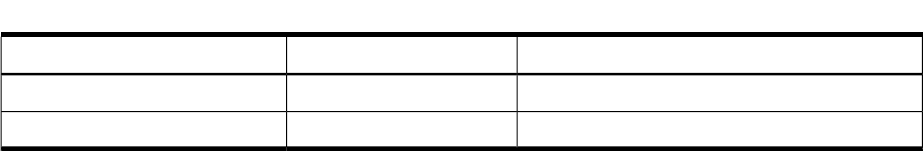

Table 1-2 Memory Array Capacities (continued)

DDR SDRAM Count, Type, and TechnologySingle DIMM SizeMininum/Maximum Memory Size

36 x 128 MB x 4 DDR1 SDRAMs (512 MB)2048 MB DIMM8 GB / 24 GB

36 x 256 MB x 4 DDR1 SDRAMs (1024 MB)4096 MB DIMM32 GB / 32 GB

Chip Spare Functionality

Chip spare enables an entire DDR SDRAM chip on a DIMM to be bypassed in the event that a

multi-bit error is detected on the DDR SDRAM. To use the chip spare functionality on your

server, use only DIMMs built with ×4 DDR SDRAM parts, and load these DIMMs in quads.

The memory subsystem design supports the I/O ASIC chip spare functionality. Chip spare enables

an entire SDRAM chip on a DIMM to be bypassed/replaced in the event that a multi-bit error is

detected on that SDRAM. To use the chip spare functionality, use only DIMMs built with x4

SDRAM parts, and load these DIMMs in quads (two DIMMs per memory cell, loaded in the

same location in each memory cell). Each DIMM within a quad must be identical to all the other

DIMMs in the quad.

Chip spare is achieved if four identical DIMMs are loaded into a quad. If more DIMMs are added,

they must be loaded in quads to maintain the chip spare functionality. So, if more DIMMs are

added in to the example case, four identical DIMMs (identical to each other, but can be different

from the original quad that was loaded) must be loaded into the next quad. However, if you are

using 4 GB DIMMS, the only configuration supported is eight 4 GB DIMMS in the first three

quads, with no other DIMMs in the remaining quad. For slot and quad locations, see Figure 4-23

(page 58).

Serial Presence Detect

Each DIMM contains an I2C electronically erasable programmable read-only memory (EEPROM)

whose content describes the module characteristics. This feature is called serial presence detect

(SPD). Firmware typically uses this information to detect unmatched pairs of DIMMs and

configure certain memory subsystem parameters. The SPD information for DIMMs loaded in

the server is also accessible to the BMC through the I2C bus.

I/O Bus Interface

The I/O bus interface provides these features:

• Industry-standard PCI 33 MHz and 66 MHz, PCI-X 66 MHz to 133 MHz, 32 or 64 data bit

support

• 3.3 V PCI only (does not support 5 V PCI)

• DMA performance optimization

• 3.3 V or Universal keyed PCI card support (not 5 V keyed PCI cards)

• Up to four PCI sockets

Processor Dependent Hardware Controller

The PDH controller provides these features:

• 16-bit PDH bus with reserved address space for the following:

• Flash memory—

— Nonvolatile memory

— Scratch RAM

— Real-time Clock

— UARTs

— External registers

— Firmware read/writable registers

System Board Components 25