Chapter 2 Configuration and Installation

© National Instruments Corporation 2-17 Lab-NB User Manual

Timing Connections

Pins 38 through 48 of the I/O connector are connections for timing I/O signals. The timing I/O of

the Lab-NB is designed around the 8253 Counter/Timer integrated circuit. Two of these integrated

circuits are employed in the Lab-NB. One, designated 8253(A), is used exclusively for DAQ

timing, and the other, 8253(B), is available for general use. Pins 38 through 40 carry external

signals that can be used for DAQ timing in place of the dedicated 8253(A). These signals are

explained under DAQ Timing Connections later in this chapter. Pins 41 through 48 carry general-

purpose timing signals from 8253(B). These signals are explained under General-Purpose

Timing Connections later in this chapter.

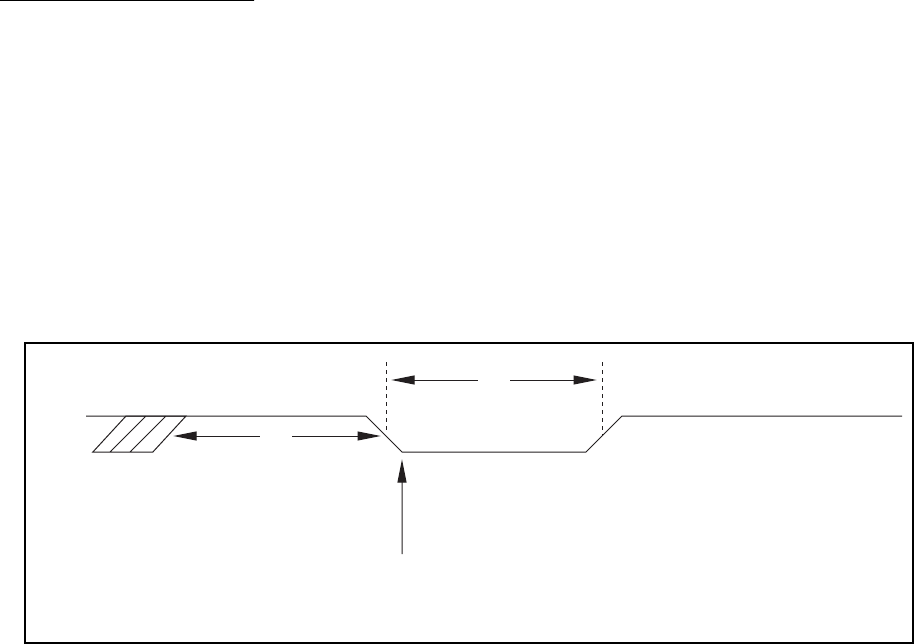

DAQ Timing Connections

Counter 0 on the 8253(A) Counter/Timer (referred to as A0) is used as a sample-interval counter

in timed A/D conversions. Counter 1 on the 8253(B) Counter/Timer (referred to as A1) is used as

a sample counter in conjunction with counter 0 for data acquisition. These counters are not

available for general use. In addition to counter A0, EXTCONV* can be used to externally time

conversions. See Chapter 4, Register-Level Programming, for the programming sequence needed

to enable this input. Figure 2-10 shows the timing requirements for the EXTCONV* input. An

A/D conversion is initiated by a falling edge on the EXTCONV*. If EXTCONV* stays low

more than 12

µsec, the data from this conversion is not latched into the FIFO memory until the

following rising edge on EXTCONV*. If EXTCONV* stays low less than 12

µsec, the data from

this conversion is latched into the FIFO memory after 12

µsec.

A/D Conversion starts within

125 nsec from this point

EXTCONV*

t

w

250 nsec minimum

(worst-case)

(100 nsec typical)

V

IH

V

IL

t

w

t

w

Figure 2-10. EXTCONV* Signal Timing

Another external control, EXTTRIG, is used for either starting a DAQ sequence or terminating an

ongoing DAQ sequence, depending on the settings of the EXTTRIGEN and PRETRIG bits in the

ADC Configuration Register.

If EXTTRIGEN is set, EXTTRIG serves as an external trigger to start a DAQ sequence. In this

mode, posttrigger mode, the sample-interval counter is gated off until a rising edge is sensed on

the EXTTRIG line. EXTCONV*, however, is enabled on the first rising edge of EXTCONV*,

following the rising edge on the EXTTRIG line. Further transitions on the EXTTRIG line have no