Configuration and Installation Chapter 2

Lab-NB User Manual 2-18 © National Instruments Corporation

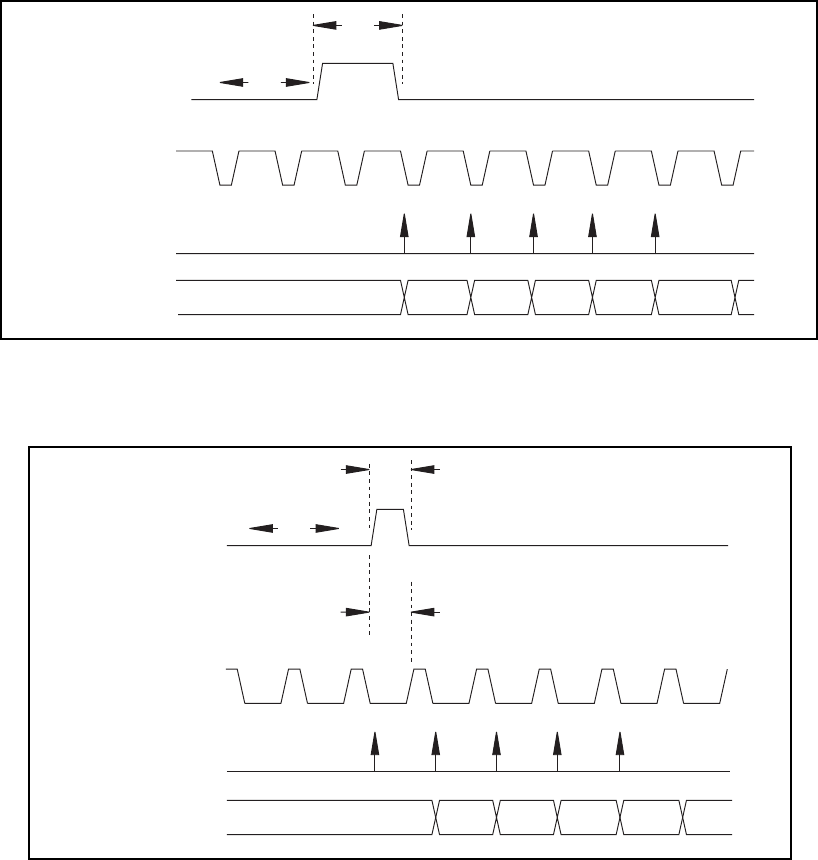

effect until a new DAQ sequence is established. Figures 2-11 and 2-12 illustrate two possible

posttrigger DAQ timing cases. In Figure 2-11, the rising edge on EXTTRIG is sensed when the

EXTCONV* input is high. Thus, the first A/D conversion occurs on the second falling edge of

EXTCONV*, after the rising edge on EXTTRIG. In Figure 2-12, the rising edge on EXTTRIG is

sensed when the EXTCONV* input is low. In this case, the first A/D conversion occurs on the

first falling edge of EXTCONV*, after the rising edge on EXTTRIG. Notice that Figures 2-11

and 2-12 show a controlled acquisition mode DAQ sequence; that is, Sample Counter A1 disables

further A/D conversions after the programmed count (3 in the examples shown in Figures 2-11

and 2-12) expires. The counter is not loaded with the programmed count until the first falling edge

following a rising edge on the clock input; therefore two extra conversion pulses are generated as

shown in Figures 2-11 and 2-12. EXTTRIG can also be used as an external trigger in freerun

acquisition mode.

t

w

50 nsec minimum

EXTTRIG

EXTCONV*

CONVERT

V

IH

V

IL

t

w

t

w

Sample

Counter

XX3210

Figure 2-11. Posttrigger DAQ Timing

(EXTCONV* High When Trigger Sensed)

t

w

50 nsec minimum

EXTTRIG

V

IH

V

IL

t

w

EXTCONV*

CONVERT

t

d

50 nsec minimum

t

w

Sample

Counter

X 3210

Figure 2-12. Posttrigger DAQ Timing

(EXTCONV* Low When Trigger Sensed)