Chapter 4 Signal Connections

PCI-6110E/6111E User Manual 4-4

©

National Instruments Corporation

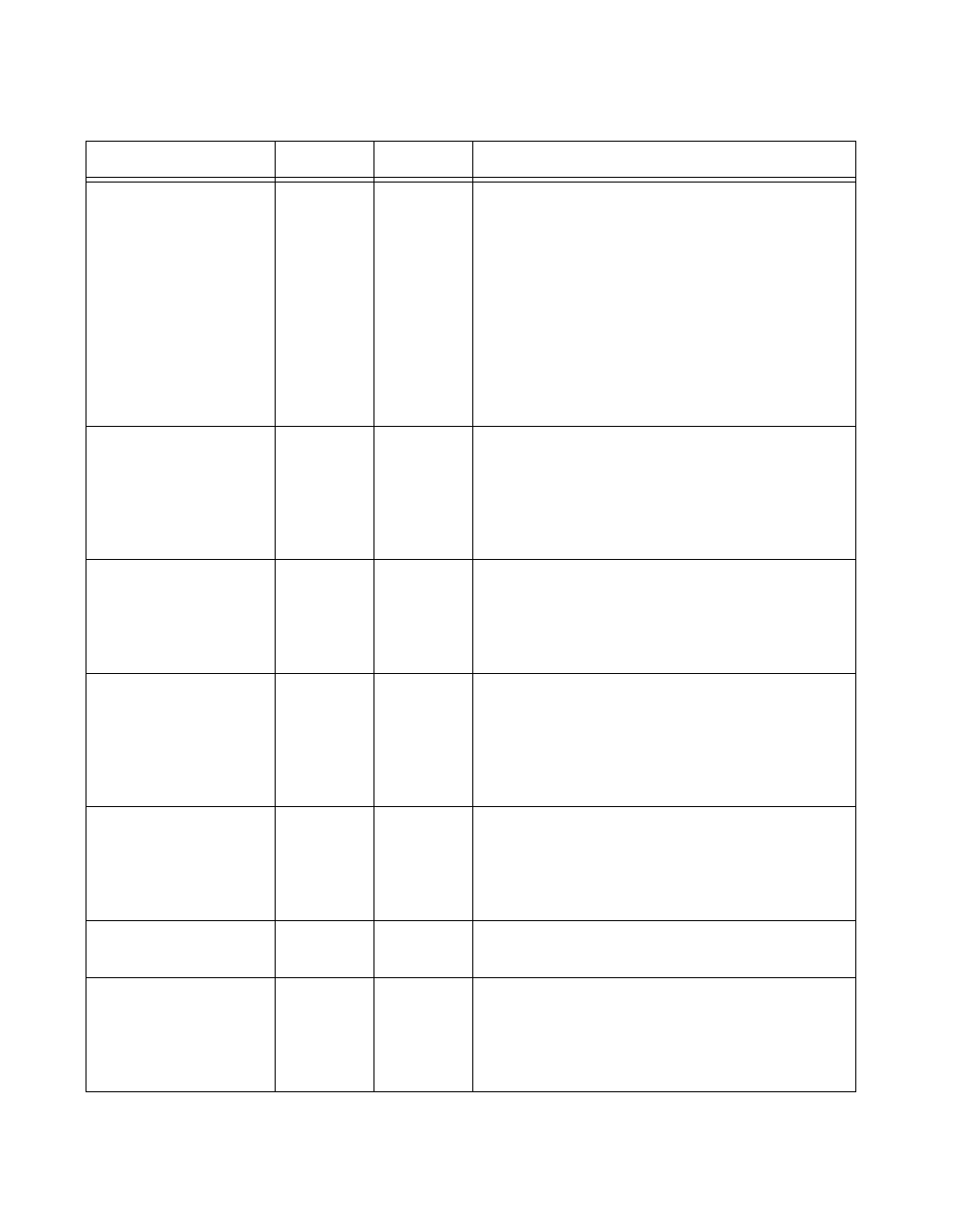

PFI0/TRIG1 DGND Input

Output

PFI0/Trigger 1—As an input, this is either one of the

Programmable Function Inputs (PFIs) or the source for the

hardware analog trigger. PFI signals are explained in the

Timing Connections section later in this chapter. The

hardware analog trigger is explained in the Analog Trigger

section in Chapter 3, Hardware Overview.

As an output, this is the TRIG1 signal. In posttrigger data

acquisition sequences, a low-to-high transition indicates the

initiation of the acquisition sequence. In pretrigger

applications, a low-to-high transition indicates the initiation

of the pretrigger conversions.

PFI1/TRIG2 DGND Input

Output

PFI1/Trigger 2—As an input, this is one of the PFIs.

As an output, this is the TRIG2 signal. In pretrigger

applications, a low-to-high transition indicates the initiation

of the posttrigger conversions. TRIG2 is not used in

posttrigger applications.

PFI2/CONVERT* DGND Input

Output

PFI2/Convert—As an input, this is one of the PFIs.

As an output, this is the CONVERT* signal. A high-to-low

edge on CONVERT* indicates that an A/D conversion is

occurring.

PFI3/GPCTR1_SOURCE DGND Input

Output

PFI3/Counter 1 Source—As an input, this is one of the

PFIs.

As an output, this is the GPCTR1_SOURCE signal. This

signal reflects the actual source connected to the

general-purpose counter 1.

PFI4/GPCTR1_GATE DGND Input

Output

PFI4/Counter 1 Gate—As an input, this is one of the PFIs.

As an output, this is the GPCTR1_GATE signal. This signal

reflects the actual gate signal connected to the

general-purpose counter 1.

GPCTR1_OUT DGND Output Counter 1 Output—This output is from the general-purpose

counter 1 output.

PFI5/UPDATE* DGND Input

Output

PFI5/Update—As an input, this is one of the PFIs.

As an output, this is the UPDATE* signal. A high-to-low

edge on UPDATE* indicates that the analog output primary

group is being updated.

Table 4-1. Signal Descriptions for I/O Connector Pins (Continued)

Signal Name Reference Direction Description

PCI_E.book Page 4 Thursday, June 25, 1998 12:55 PM