Chapter 4 Signal Connections

©

National Instruments Corporation 4-21 PCI-6110E/6111E User Manual

of scans before TRIG2 can be recognized. After the scan counter

decrements to zero, it is loaded with the number of posttrigger scans to

acquire while the acquisition continues. The board ignores the TRIG2

signal if it is asserted prior to the scan counter decrementing to zero.

After the selected edge of TRIG2 is received, the board will acquire a

fixed number of scans and the acquisition will stop. This mode acquires

data both before and after receiving TRIG2.

As an output, the TRIG2 signal reflects the posttrigger in a pretriggered

acquisition sequence. This is true even if the acquisition is being

externally triggered by another PFI. The TRIG2 signal is not used in

posttriggered data acquisition. The output is an active high pulse with a

pulse width of 25 to 50 ns. This output is set to tri-state at startup.

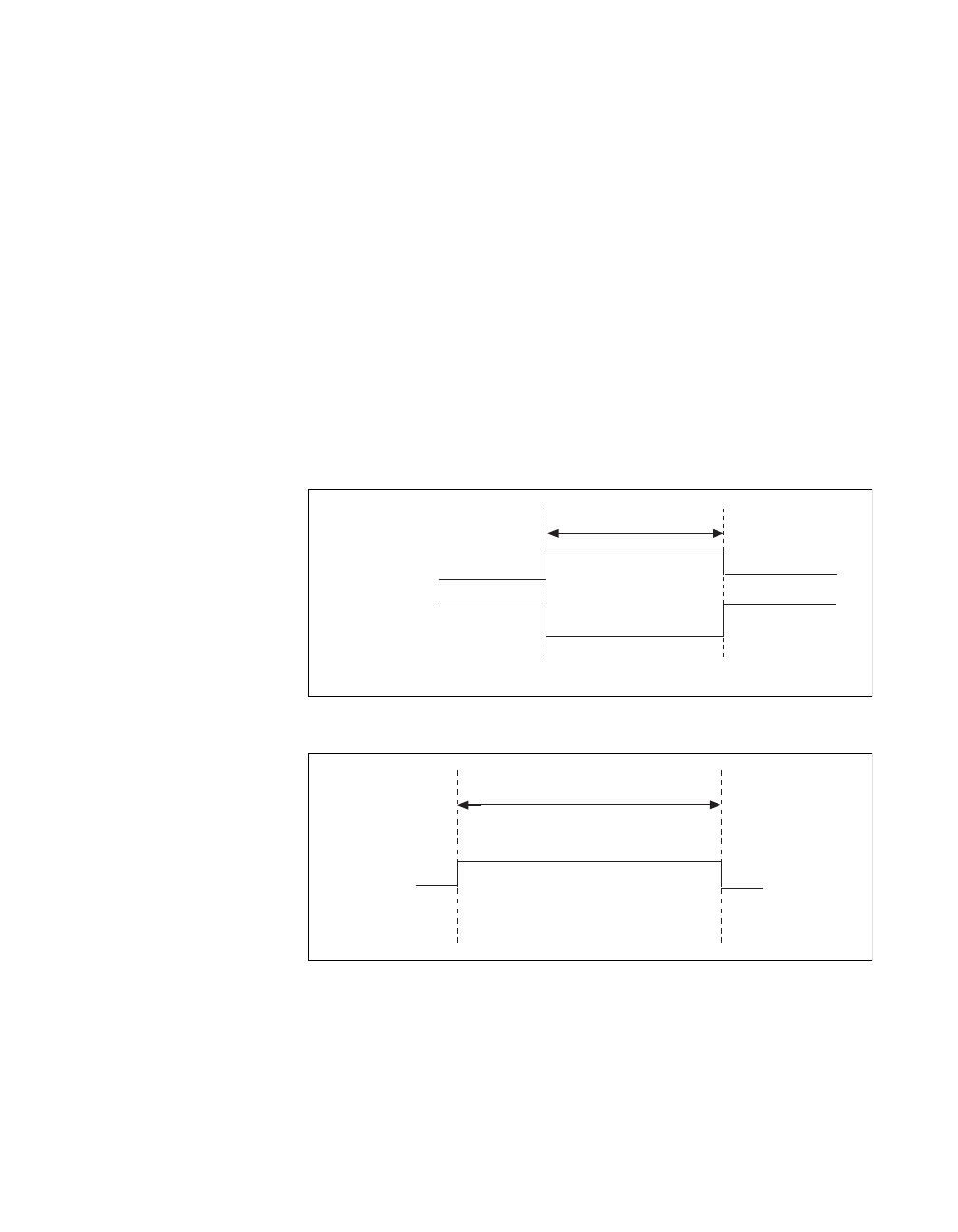

Figures 4-14 and 4-15 show the input and output timing requirements

for the TRIG2 signal.

Figure 4-14. TRIG2 Input Signal Timing

Figure 4-15. TRIG2 Output Signal Timing

Rising-edge

polarity

Falling-edge

polarity

t

w

t

w

= 10 ns minimum

t

w

t

w

= 25-50 ns

PCI_E.book Page 21 Thursday, June 25, 1998 12:55 PM