Chapter 4 Signal Connections

©

National Instruments Corporation 4-31 PCI-6110E/6111E User Manual

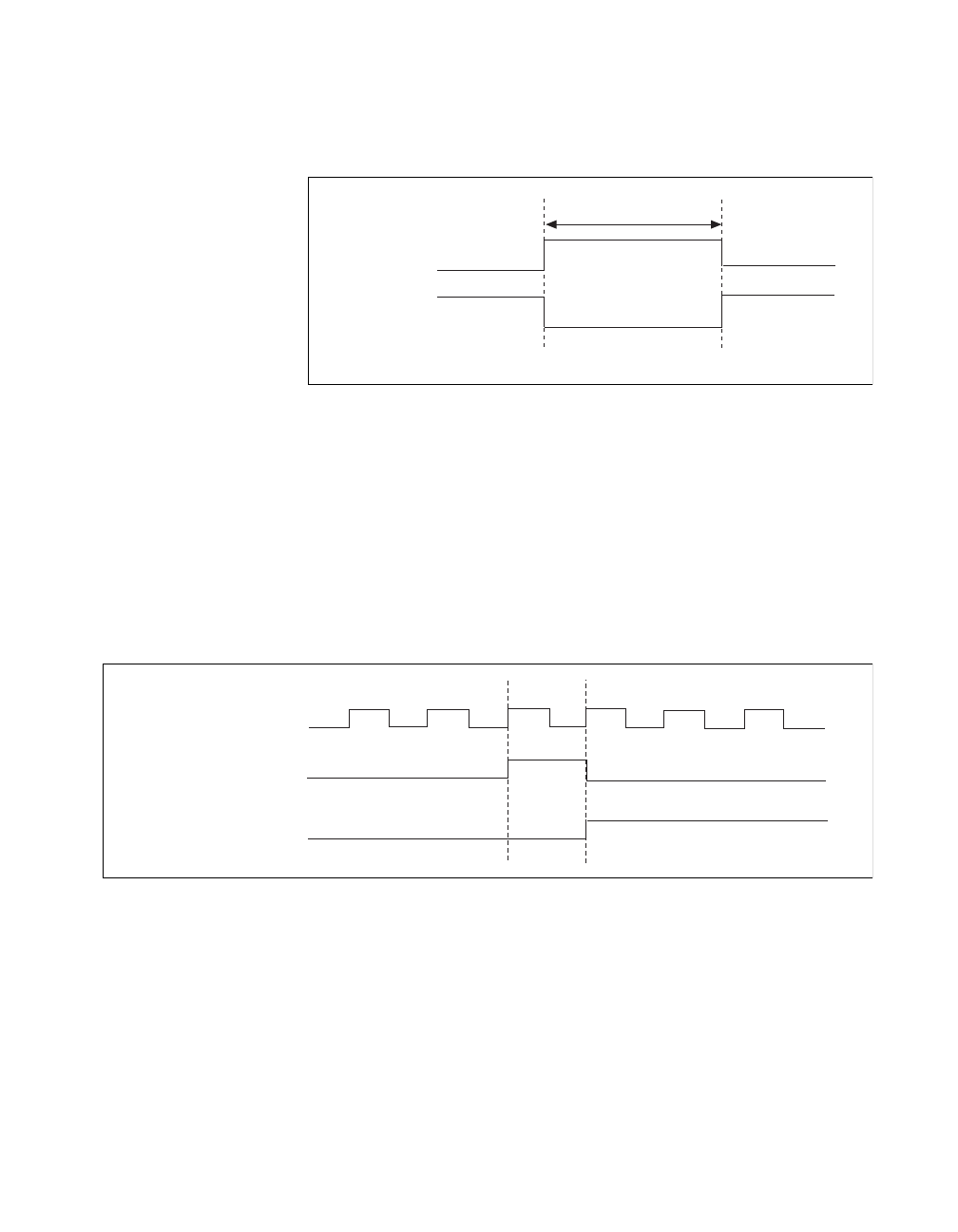

Figure 4-27 shows the timing requirements for the GPCTR0_GATE

signal.

Figure 4-27. GPCTR0_GATE Signal Timing in Edge-Detection Mode

GPCTR0_OUT Signal

This signal is available only as an output on the GPCTR0_OUT pin.

The GPCTR0_OUT signal reflects the terminal count (TC) of

general-purpose counter 0. You have two software-selectable output

options—pulse on TC and toggle output polarity on TC. The output

polarity is software selectable for both options. This output is set to

tri-state at startup. Figure 4-28 shows the timing of the GPCTR0_OUT

signal.

Figure 4-28. GPCTR0_OUT Signal Timing

GPCTR0_UP_DOWN Signal

This signal can be externally input on the DIO6 pin and is not available

as an output on the I/O connector. The general-purpose counter 0 will

count down when this pin is at a logic low and count up when it is at a

logic high. You can disable this input so that software can control the

up-down functionality and leave the DIO6 pin free for general use.

Rising-edge

polarity

Falling-edge

polarity

t

w

t

w

= 10 ns minimum

GPCTR0_SOURCE

GPCTR0_OUT

GPCTR0_OUT

(Toggle output on TC)

(Pulse on TC)

TC

PCI_E.book Page 31 Thursday, June 25, 1998 12:55 PM