292

Execution of a step is completed either by execution of the next SNXT(09) or by

turning OFF the control bit for the step (see example 3 below). When the step is

completed, all of the IR and HR bits in the step are turned OFF. All timers in the

step except TTIM(––) are reset to their SVs. TTIM(––), counters, shift registers,

bits set or reset with SET or RSET, and bits used in KEEP(11) maintain status.

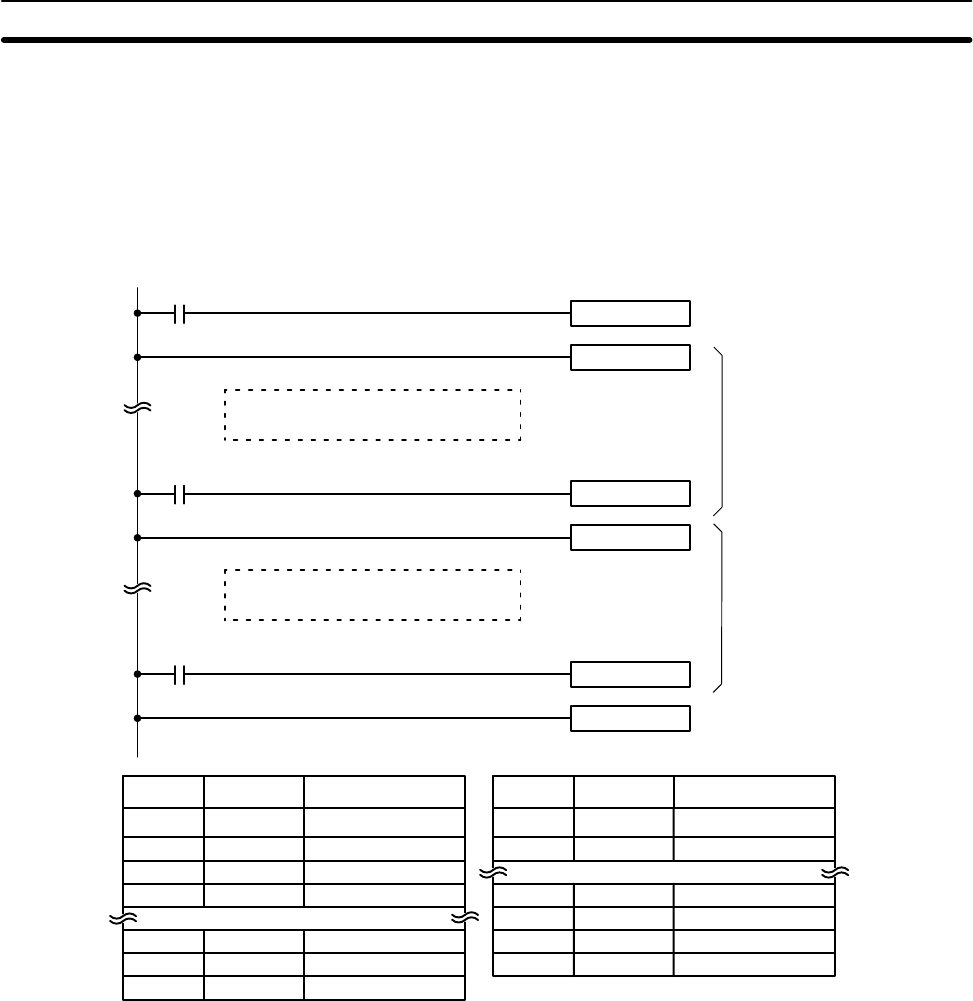

Two simple steps are shown below.

SNXT(09) LR 2000

STEP(08) LR 2000

00000

Step controlled by LR 2000

SNXT(09) LR 2001

STEP(08) LR 2001

00001

Step controlled by LR 2001

SNXT(09) LR 2002

STEP(08)

00002

Starts step execution

Ends step execution

1st step

2nd step

Address Instruction Operands Address Instruction Operands

00000 LD 00000

00001 SNXT(09) LR 2000

00002 STEP(08) LR 2000

Step controlled by LR 2000

00100 LD 00001

00101 SNXT(09) LR 2001

00102 STEP(08) LR 2001

Step controlled by LR 2001

00200 LD 00002

00201 SNXT(09) LR 2002

00202 STEP(08) ---

Steps can be programmed in consecutively. Each step must start with STEP(08)

and generally ends with SNXT(09) (see example 3, below, for an exception).

When steps are programmed in series, three types of execution are possible:

sequential, branching, or parallel. The execution conditions for, and the position-

ing of, SNXT(09) determine how the steps are executed. The three examples

given below demonstrate these three types of step execution.

Precautions Interlocks, jumps, SBN(92), and END(01) cannot be used within step programs.

Bits used as control bits must not be used anywhere else in the program unless

they are being used to control the operation of the step (see example 3, below).

All control bits must be in the same word and must be consecutive.

If IR or LR bits are used for control bits, their status will be lost during any power

interruption. If it is necessary to maintain status to resume execution at the same

step, HR bits must be used.

Step Instructions Section 5-24