SMSC LAN91C111 32/16/8-Bit Three-In-One Fast Ethernet Controller

SMSC AN 9.6 19 Revision 1.0 (08-14-08)

APPLICATION NOTE

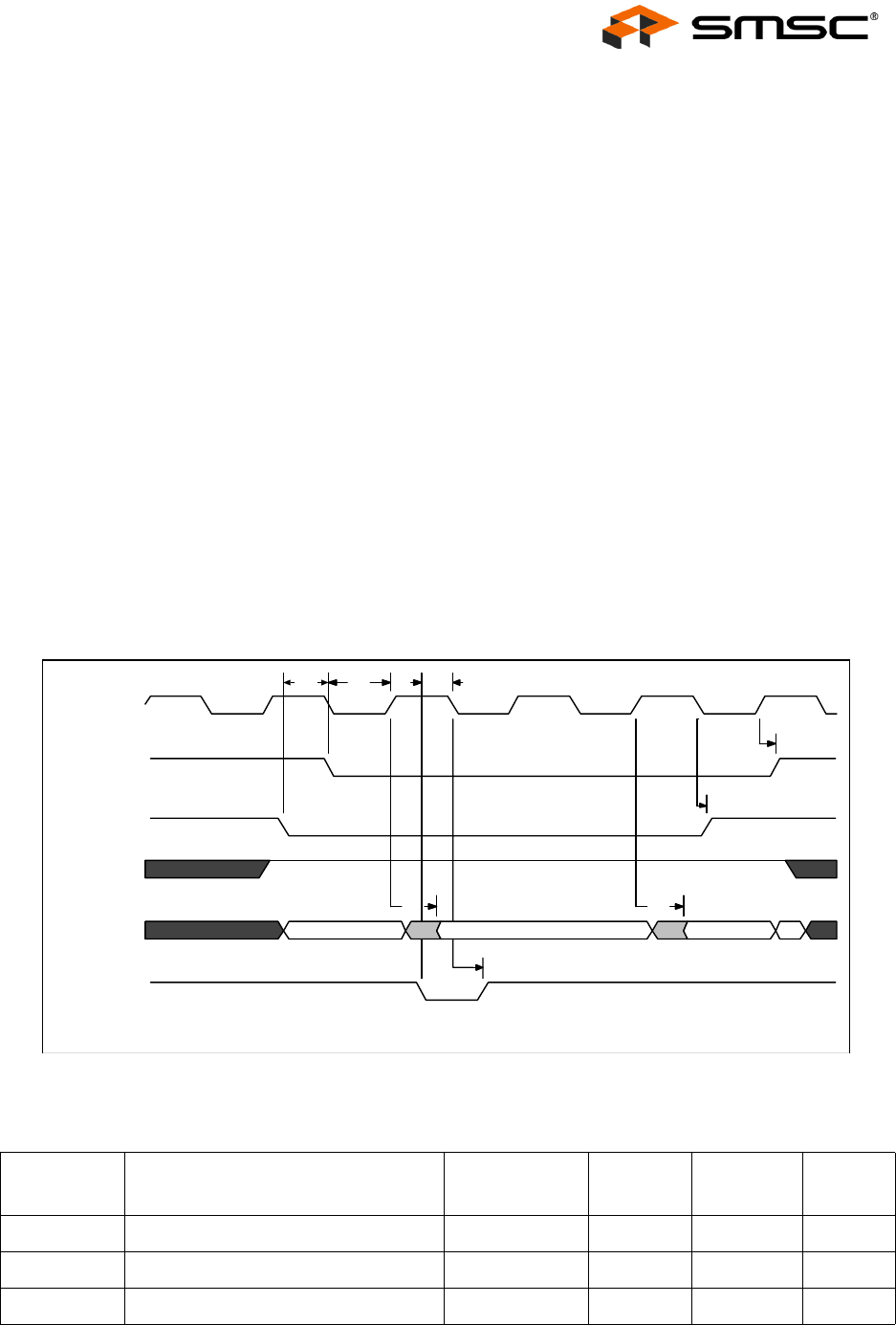

This timing diagram examples and details a burst mode write operation. The nDATACS pin remains

asserted throughout the cycle and the nCYCLE pin is used to control the burst data. As long as

nCYCLE remains asserted, data can be written on each rising edge of LCLK.

In the above timing diagram nRDYRTN is used to insert a wait state between the second and third

data packet. The assertion of nRDYRTN is required at a minimum of 10nS before the falling edge of

LCLK to insert the wait state. A wait state will be held as long as nRDYRTN remains asserted. In the

above example a single wait cycle is inserted between the second and third packet of data. More wait

states can be inserted by holding nRDYRTN asserted for another LCLK cycle. nRDYRTN only needs

to remain asserted for 10nS after the falling edge of LCLK. Once the state machine sees the asserted

nRDYRTN it will automatically insert the wait state.

Data is written on the rising edge of LCLK and needs to be stable 15nS prior to this rising edge. Data

also needs to remain stable for 4nS after the rising edge to ensure that the data was properly written.

By using the Auto-Increment mode of operation it is possible to completely fill the FIFO’s with minimum

overhead to the system. Once a write operation is started you can simply pump data into the FIFO’s

for transmission out the Ethernet port.

3.11 Burst Mode Read Operation

The timing diagram below details a burst mode read operation and shows three separate packets of

data being transferred. In this example there is a delay between the first and second packet of data

being read. This delay is being accomplished using the nRDYRTN signal as in the Burst Mode Write

Operation.

Figure 3.10 Burst Mode Read Operation

PARAMETER

MIN TYP MAX UNITS

t12 nDATACS Setup to LCLK Rising 20 ns

t12A nDATACS Hold after LCLK Rising 0 ns

t14 nRDYRTN Setup to LCLK Falling 10 ns

t15

t

19t19

t17A

t

12A

t14t12t17

abc

Clock

n

DATACS

W/nR

nCYCLE

R

ead Data

n

RDYRTN