SMSC LAN91C111 32/16/8-Bit Three-In-One Fast Ethernet Controller

SMSC AN 9.6 5 Revision 1.0 (08-14-08)

APPLICATION NOTE

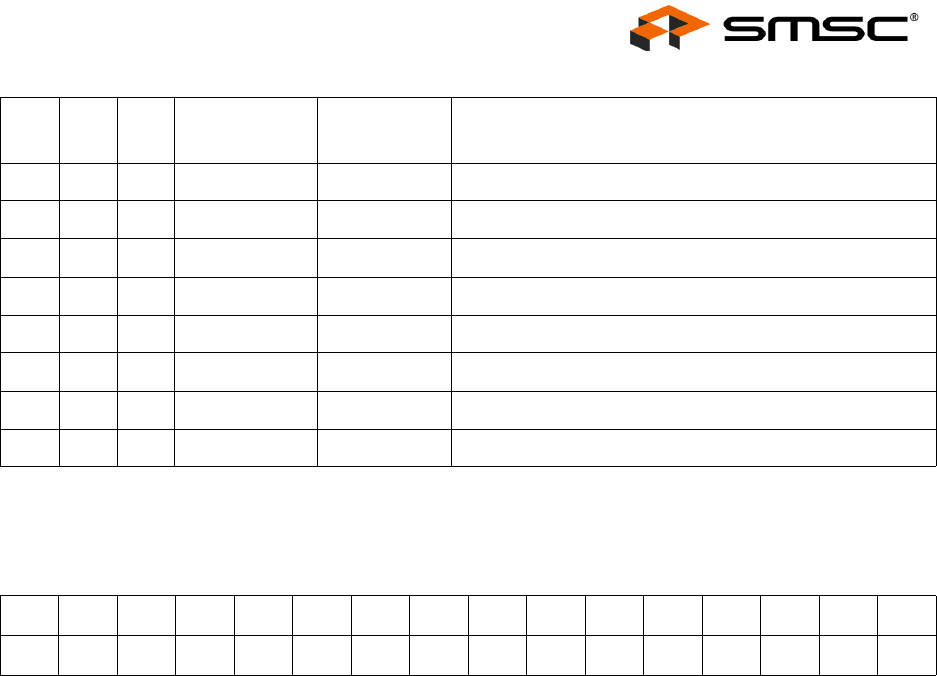

3.3.1 Address Decoding Example

3.3.2 I/O Base Address 300h Decoding

The chart below shows the decoding of I/O Base Address 300h:

3.4 Asynchronous Interface

When the LAN91C111 working with an asynchronous bus, the read and write operation are controlled

by the edges of nRD and nWR. ARDY is used for notifying the system that it should extend the access

cycle. The leading edge of ARDY is generated by the leading edge of nRD or nWR while the trailing

edge of ARDY is controlled by the internal LAN91C111 clock and, therefore, asynchronous to the bus.

A3 A2 A1 IO-ADDRESS

BYTE

ENABLE NOTES

0 0 0 300 nBE0 Assert nBE0 to enable the lowest byte

0 0 0 301 nBE1 Assert nBE1 to enable the second lowest byte

0 0 1 302 nBE0 Assert nBE0 to enable the lowest byte

0 0 1 303 nBE1 Assert nBE1 to enable the second lowest byte

0 1 0 304 nBE0 Assert nBE0 to enable the lowest byte

0 1 0 305 nBE1 Assert nBE1 to enable the second lowest byte

0 1 1 306 nBE0 Assert nBE0 to enable the lowest byte

0 1 1 307 nBE1 Assert nBE1 to enable the second lowest byte

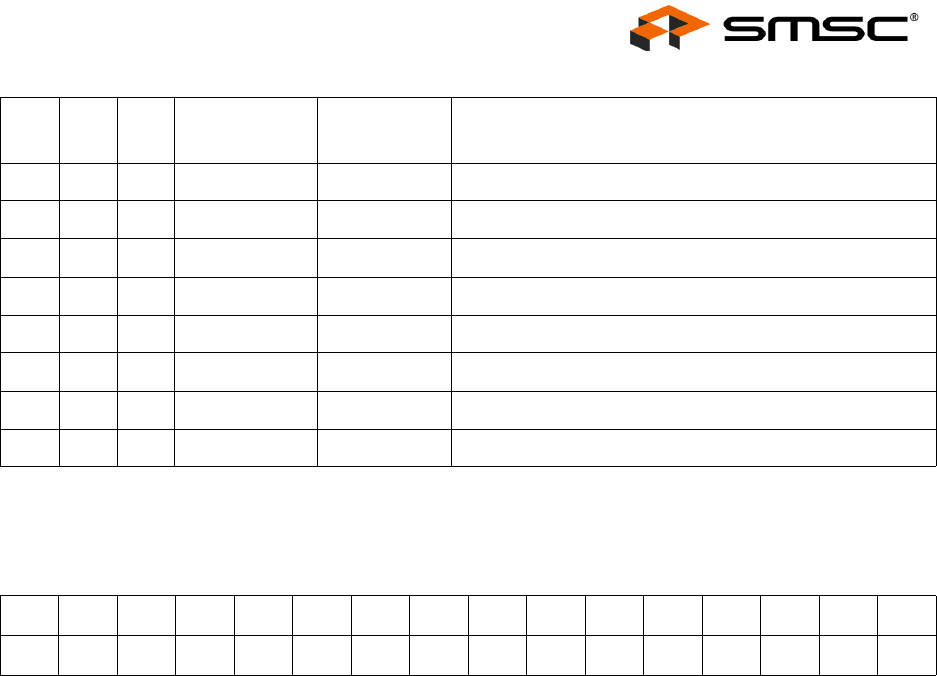

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0000001100000000