Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer 27

Technical Product Specification

Hardware Management Overview

Hardware Management Overview 3

The Intelligent Platform Management Controller (IPMC) is an Intel-designed baseboard

management controller device manufactured by Philips Semiconductor* for Intel.

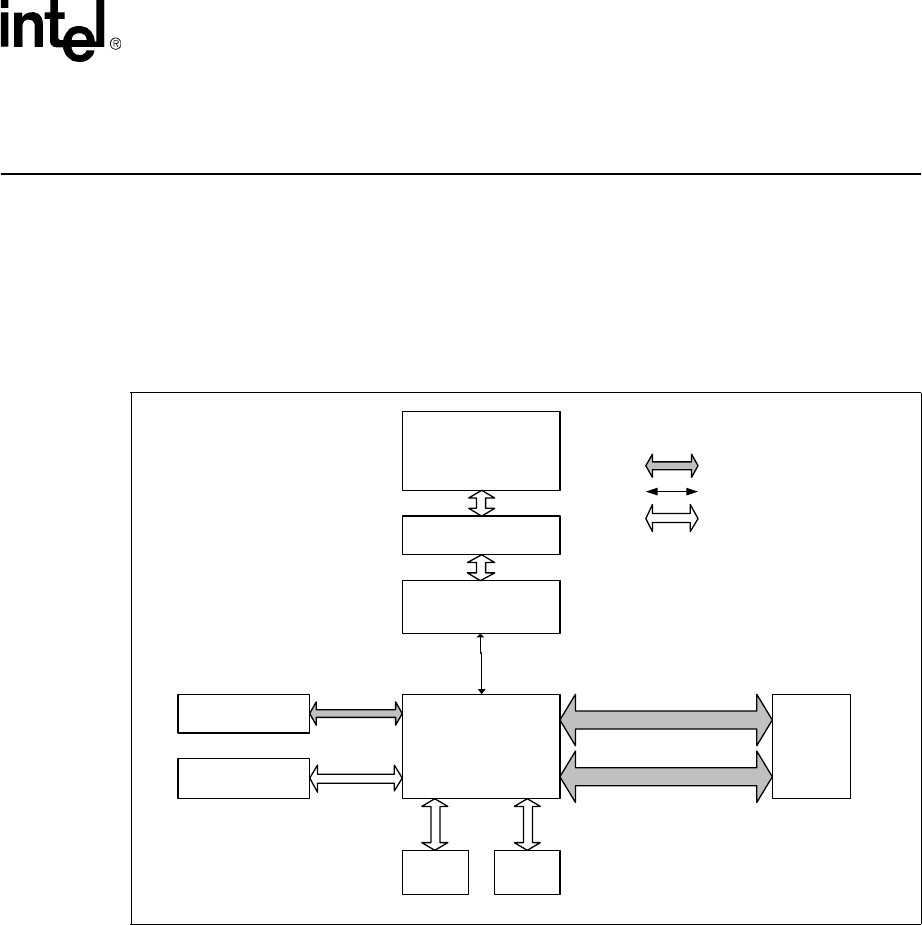

The high-level architecture of the baseboard management for MPCBL0001 is represented in the

block diagram below.

The main processors communicate with the IPMC using the Keyboard Controller Style (KCS)

interface. Two KCS interfaces are available for the BIOS to communicate to the IPMC. BIOS uses

SMS interface for normal communication and SMM interface when executing code under systems

management mode (SMM). The base address of the LPC interface for SMS is 0xCA2 and 0xCA4

for SMM operation. Besides that, the BIOS is able to communicate with the IPMC for POST error

logging purposes, fault resilient purposes, and critical interrupts via the KCS interface.

The memory subsystem of the IPMC consists of a flash memory to hold the IPMC operation code,

firmware update code, system event log (SEL), and a sensor data record (SDR) repository. RAM is

used for data and occasionally as a storage area for code when flash programming is under

execution. The field replacement unit (FRU) inventory information is stored in the nonvolatile

memory on ADM1026. The flash memory can store up to 64 KBytes of SEL events and SDR

information, while the ADM1026 can store up to 512 bytes of FRU information. Having the SEL

and logging functions managed by the IPMC helps ensure that ‘post-mortem’ logging information

is available even if the system processor becomes disabled.

Figure 3. Hardware Management Block Diagram

Intelligent Platform

Management Controller

(IPMC)

Backplane

(P10)

IPMB A

I

P

M

B

B

ADM 1026

SRAM

Flash

Memory

Watchdog Timer

ICH3

CPU

(Low Voltage Intel

®

Xeon™)

Intel

®

E7501 Memory

Controller Hub (MCH)

I2C Bus

Logic C onnect ion

KCS interf ace

NOTE: