Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer 59

Technical Product Specification

Hardware Management Overview

3.12.5 Cold Boot

Any soft reset that does not meet the configuration described in the preceding Warm Boot section is

classified as a cold boot. Execution starts at the reset vector, and BIOS initializes and configures all

devices, including memory subsystem, as if a hard reset had occurred. See Table 25, “Reset

Actions” on page 59.

During a cold boot the BIOS initializes the warm reset counter to 0x0A and clears the reset flag to

1234h. Software can then read the reset flag to determine the type of reset.

3.12.6 Power Good

When the MPCBL0001 SBC is inserted into the chassis, the hardware management circuitry is

“hot plugged.” The hardware management voltage is immediately applied, and the on-board IPMC

is reset. After the hardware management reset, the operation of the IPMC and full power-up of the

SBC are under firmware control.

Upon command to power on the module, the IPMC asserts the “power enable” signal to the on-

board DC/DC converters. Full power-up of the SBC is sequenced by hardware to ensure device-

specific power requirements are followed. Sequencing of specific voltages is required to ensure

that devices using multiple voltages are not damaged or stressed.

Table 25. Reset Actions

Reset Actions System Function Memory Status

Warm boot Partial restart Preserves memory above 8MB boundary

Cold boot Full restart Functionally equivalent to a hard reset.

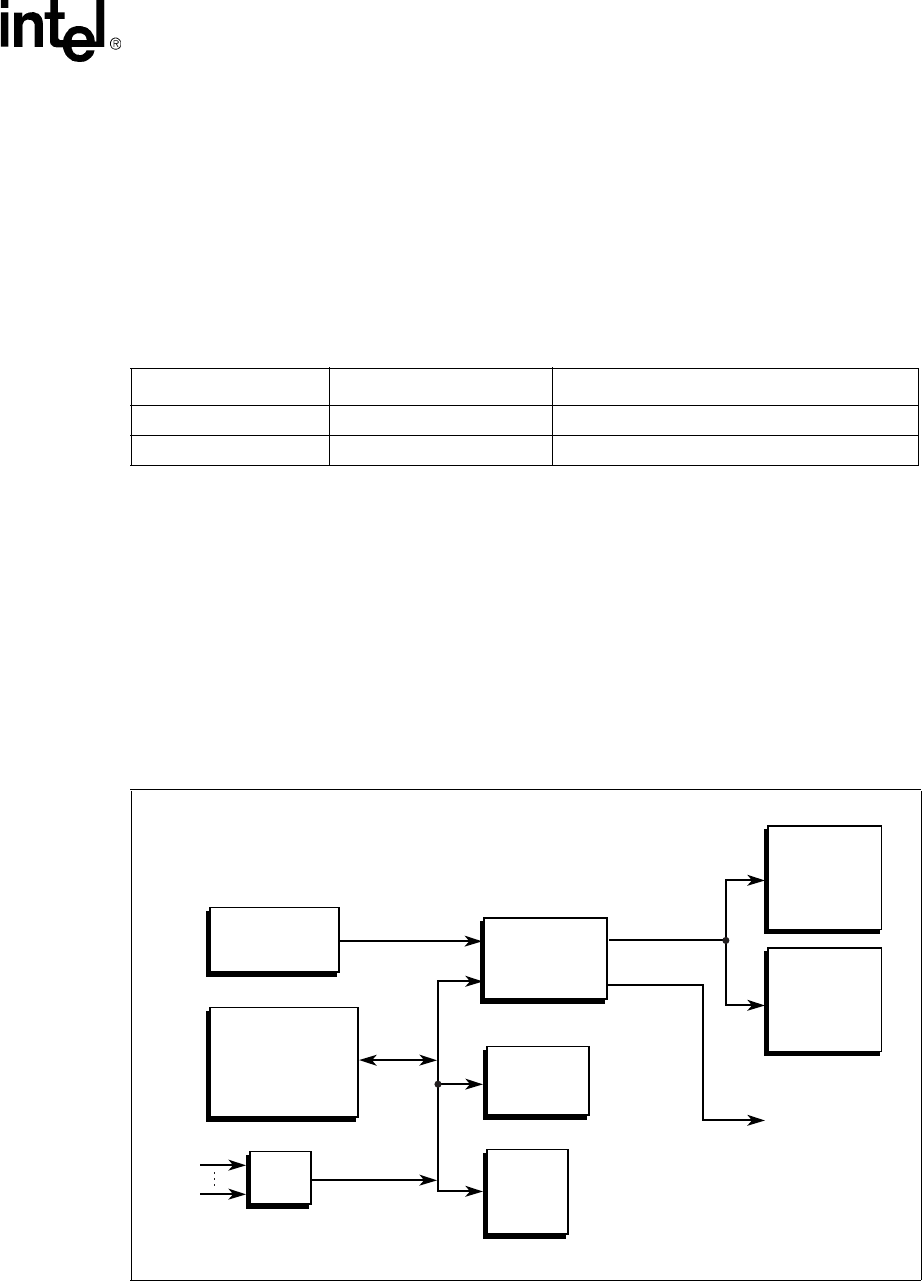

Figure 8. Power Good Map

B0895-02

VRM

Controller

ICH3

ICH3_PCIRST#

(global reset)

VRM_PWRGOOD

H_PWRGD

ICH3_PCIRST#

PLD

E7501

MCH

82546

Dual

GbEnet

ICH3_PWROK

Power

Goods

Intelligent Platform

Management

Controller

(IPMC)

Low Voltage

Intel

®

Xeon™

Processor

Low Voltage

Intel

®

Xeon™

Processor