86 Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer

Technical Product Specification

Addressing

CONFIG_DATA is a 32-bit read/write window into the PCI configuration space. The portion of

configuration space that is referenced by CONFIG_DATA is determined by the contents of

CONFIG_ADDRESS.

5.2 I/O Address Assignments

I/O port addresses are divided among the on-board devices.These devices include:

• ICH3

• ISP2312 Fibre Channel controller

• 82546 Ethernet controller

• SMSC LPC47B272 SIO

• MCH

• IPMC

Please refer to the respective device specifications for specific I/O address usage.

The MCH uses only I/O ports 0xCF8 and 0xCFC for PCI configuration cycle generation. These

registers were shown in Section 5.1.1 and Section 5.1.2. The P64H2 forwards applicable I/O

transactions to its attached PCI buses. The ISP2312 may be programmed to map its 256-byte bank

of registers to memory and/or I/O space.

Table 50 lists document references to I/O descriptions. Please refer to Appendix A, “Reference

Documents” for a list of the referenced documents and their complete titles, revisions, and

document numbers.

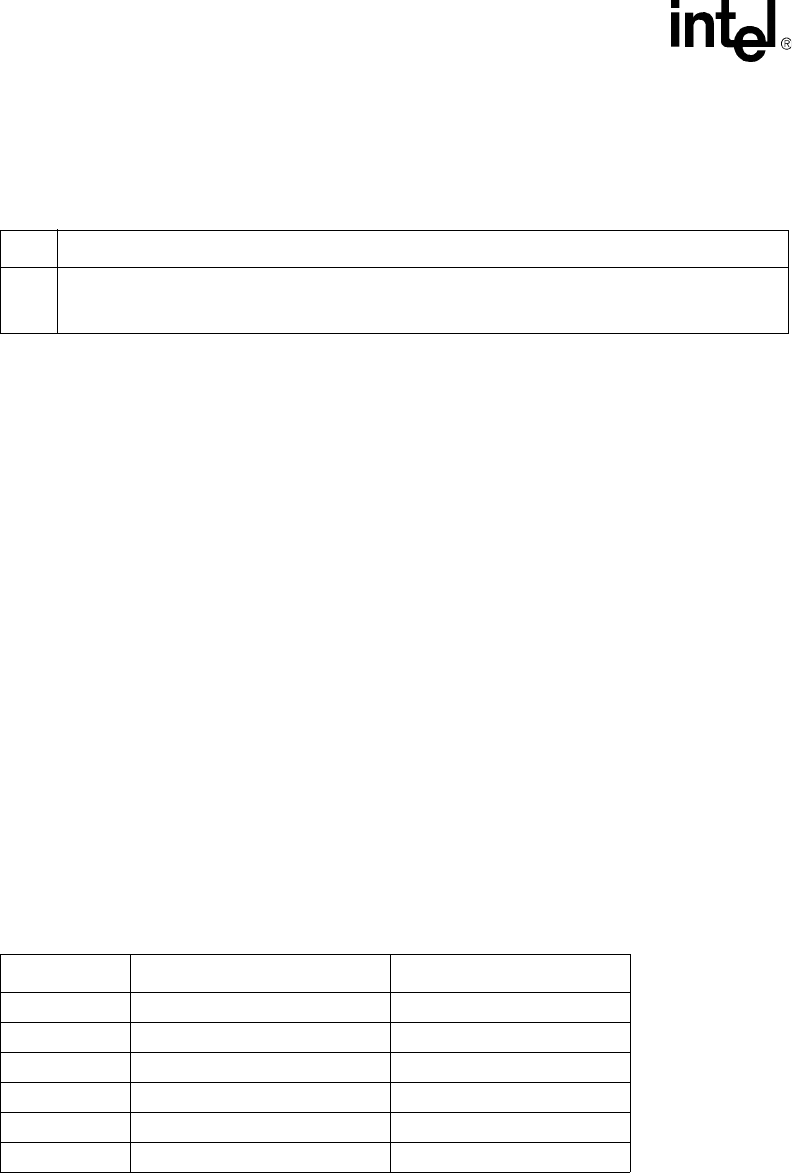

Table 49. Configuration Data Register Bit Assignments

Bit Description

31:0

Configuration Data Window (CDW): If bit 31 of CONFIG_ADDRESS is set to 1, any I/O access to

the CONFIG_DATA register is mapped to configuration space pointed to by the contents of

CONFIG_ADDRESS.

Table 50. I/O Address Cross-References

Device Document Title/Number Section/Page/Table

ICH3 ICH3 EDS Section 7.3, Table A2 and A3

MCH E7501 MCH EDS Section 4.3.5 and 4.3.6

ISP2312 ISP2312 Design Guide Section 6.6.9 and 6.7

LPC47B272 LPC47B27x Datasheet (Throughout datasheet)

IPMC Intel IPMC EDS Section 4.3.7

82546 Developer’s Manual, OR2941 Section 3.1.1.4