Intel NetStructure

®

MPCBL0001 High Performance Single Board Computer 31

Technical Product Specification

Hardware Management Overview

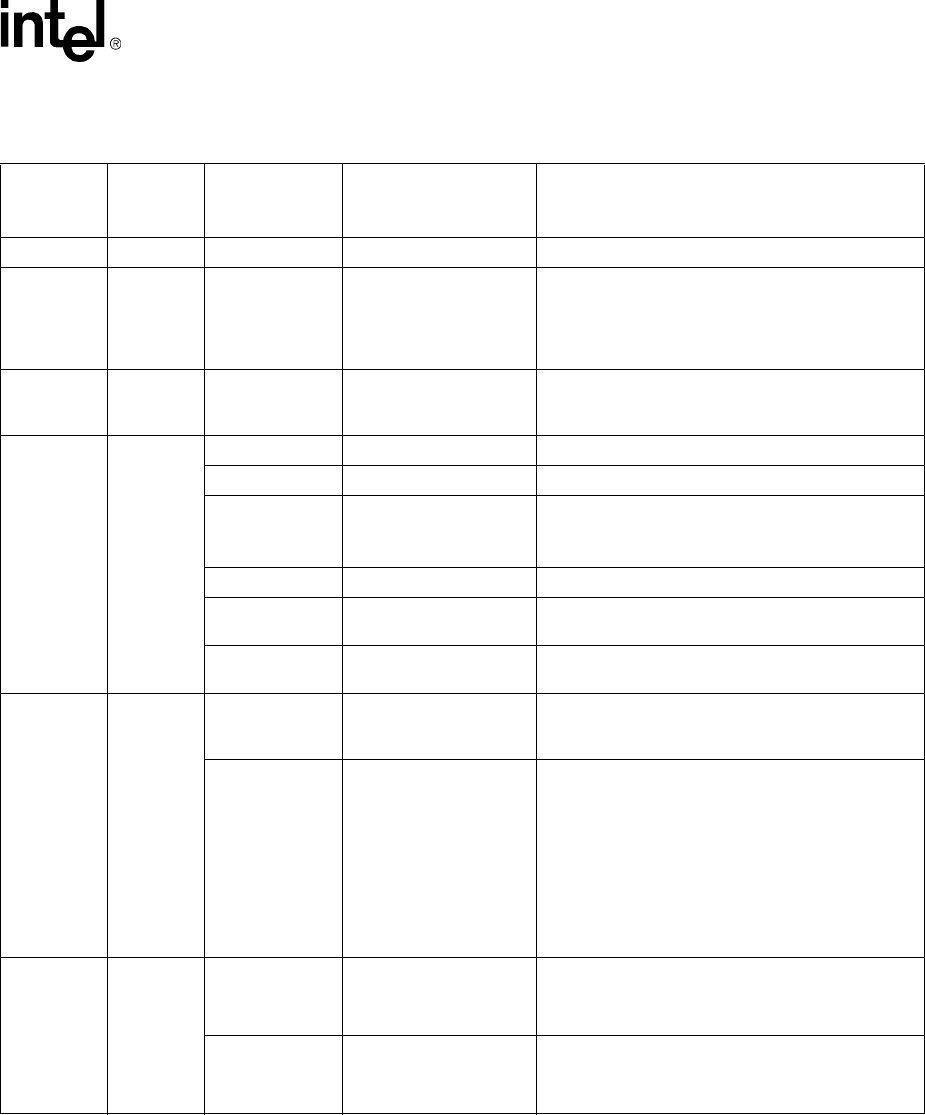

Table 3. SEL Events Supported by the MPCBL0001 SBC (Sheet 1 of 4)

Sensor

Type

Sensor

Type Code

Sensor-Specific

Offset (Event

Data 1, Bit 0-3)

Event Remarks

Reserved 00h - Reserved -

Temperature 01h - Temperature Threshold exceeded for upper critical, upper non-

critical, lower critical and lower non-critical

thresholds. Refer to Table 4, “Sensor Thresholds for

IPMC Firmware 1.0” on page 35 for sensor

thresholds data.

Voltage 02h - Voltage Voltage exceeded upper critical, upper non-critical,

lower critical and lower non-critical thresholds. Refer

to Table 4 for sensor thresholds data.

Processor 07h 00h IERR Processor IERR has occurred.

01h Thermal Trip Processor thermal trip has occurred.

04h FRB3/Processor Startup/

Initialization Failure

(CPU did not start)

An FRB3 Timer (30 seconds) was implemented to

detect the failure of the CPUs from booting.

Event data 3 = Last Post 80 code byte

05h Configuration Error CPU 0 and CPU 1 are not present.

07h Processor Presence

Detected

1

09h Terminator Presence

Detected

1

Power Unit 09h 00h Power Off/Power On Normal power off indication. Offset 0 is just a status

indicating that the payload power is off. It does not

generate an event when it is set. (For internal use).

05h Soft Power Control

Failure (unit did not

respond to request to

turn on)

The Power Unit sensor is used to detect when the

Payload power does not come up when the board is

told to power on.

When the board enters M4 state, the IPMC asserts a

Power Enable line to cause the Payload to power up.

The IPMC then waits for another line that indicates

that the power has come up successfully. If that line

does not assert within 2 seconds, then offset 05h is

asserted on the Power Unit sensor, which generates

an event to notify the Shelf Manager of the failure.

Memory 0Ch 00h Correctable ECC Event data 3 = DIMM pair number

00 refers to J8/J9

01 refers to J10/J11

01h Uncorrectable ECC Event data 3 = DIMM pair number

00 refers to J8/J9

01 refers to J10/J11

NOTE:

1. These sensor offsets do not generate events, but they are valid offsets when reading the sensor values.