OCPRF100 MP Server System Technical Product Specification

Revision 1.0

100

each region is a single address. Thus, aliases will occur on byte boundaries throughout the

remainder of the region decoded for that function. Note that the eighth region from 0xFF00 –

0xFFFF is not used.

In register bit descriptions listed below, five fields are shown: the data bit number(s), the name of

the field, how the bit(s) respond to a reset, whether the bits are readable and/or writeable, and a

description of the field. RO indicates read-only, WO indicates write-only, and RW indicates read-

able and writeable. Any fields that are marked as reserved should be ignored when read, and

should be set to zero when written.

8.6.1.3.1 Drive Fault Status Region (0xF800 – 0xF8FF)

The drive fault LEDs are controlled by this register. Writing a one to a bit turns the corresponding

LED on. Reading the register returns the current state of the LEDs. A warm or cold reset clears

all register bits to zero. The upper two bits are undefined.

8.6.1.3.2 Drive Power Enable Region (0xF900 – 0xF9FF)

Power is applied to a drive when its corresponding power-enable bit is set to one in this register.

Following a cold reset, each drive that is present will have its power-enable bit turned on. A warm

reset has no effect on this register.

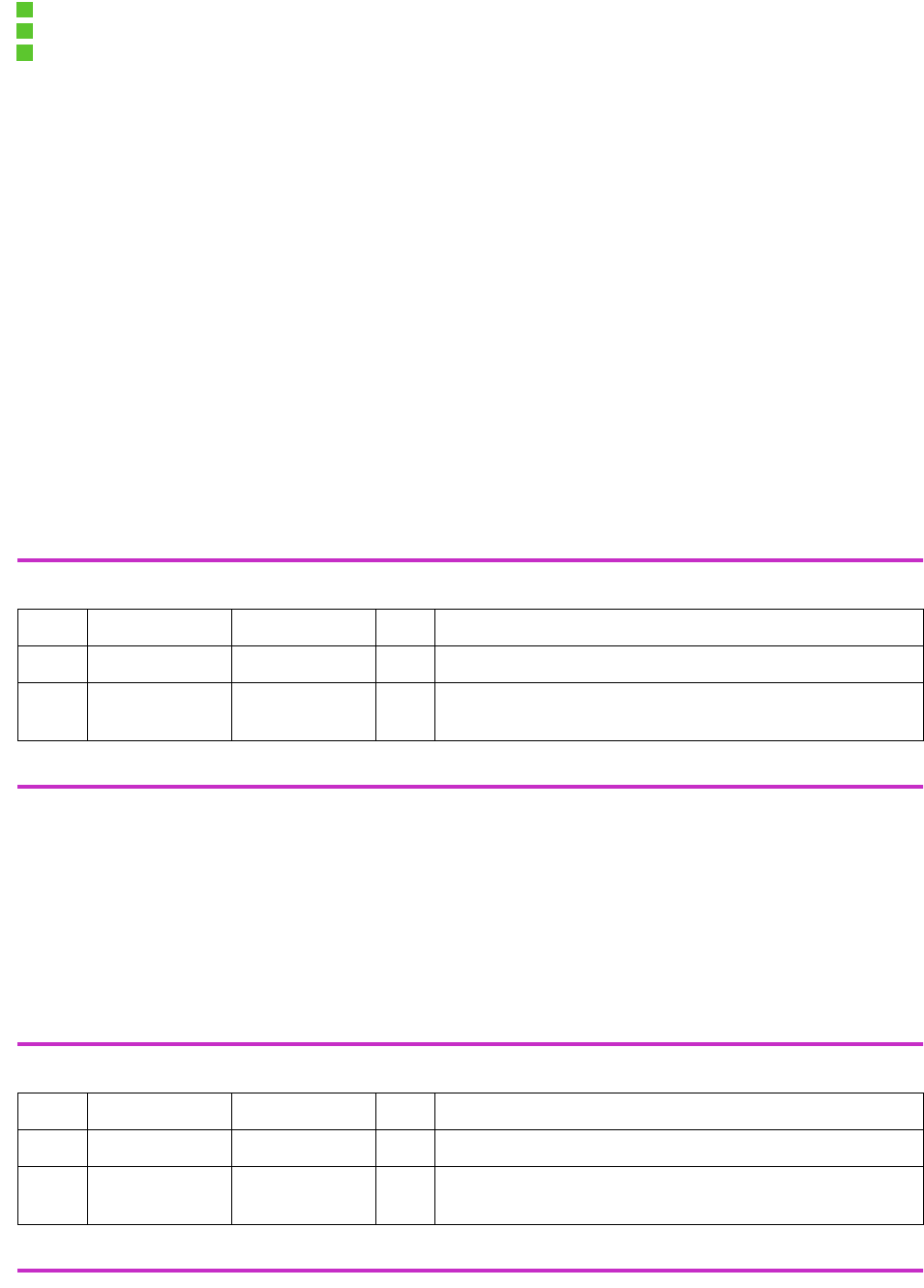

Table 8-1: Drive Fault Status Byte Format

Bit(s) Name Reset Action R/W Description

7:2 Reserved N/A Reserved bits.

1:0 FLT[1:0] Clear RW Drive fault LED enable. 0=LED off, 1=LED on. Bit 0 corre-

sponds to drive ID 0.

Table 8-2: Drive Power Enable Byte Format

Bit(s) Name Reset Action R/W Description

7:2 Reserved N/A Reserved bits.

1:0 DRVPWR[1:0] (see text) RW Drive power enable. 0=power off, 1=power on. Bit 0 corre-

sponds to drive ID 0.