OCPRF100 MP Server System Technical Product Specification

Revision 1.0

103

Notes: † “Fixed” indicates whether the function/pin is defined by the microcontroller pinout (fixed) or is implementa-

tion-specific (not fixed).

8.7 Signal Descriptions

This section defines the function of signal pins on the backplane connector interfaces.

8.7.1 Power Good Signal

This is an input signal from the OCPRF100 midplane. When asserted high, this signal signifies

that the power supplies have their PWR_GOOD asserted meaning that power has been applied

and not faulted. The PWR_GOOD signal and signal from an onboard Dallas DS1233* reset con-

troller are ORed to keep the board in reset. When both signals indicate that power is good, two

things happen: 1) the reset signals are negated to the controllers, SCSI target, and other logic;

and 2) power is sequentially applied to each SCA drive connector where a drive is present.

8.7.2 CONN_EN_L

This signal enables the programming capability. When this signal is low, the two microcontrollers

are held in reset, and the JTAG mode pin is gated through to the TMS input on the PLDs. When

this signal is high, the microcontroller reset is controlled via normal means and the TMS input to

the PLDs is held high, which keeps the JTAG interface in an idle state.

8.7.3 CONN_SDI

This is the serial data input stream into the TDI input of the first device on the JTAG chain.

8.7.4 CONN_SDO

This is the serial data output stream from the TDO output of the last device on the JTAG chain.

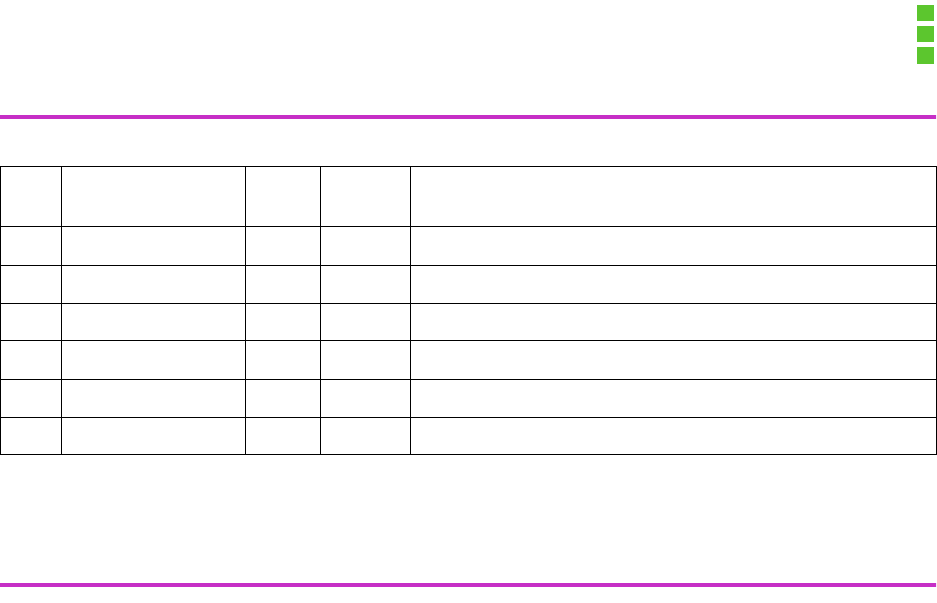

6 WR_L O Y Write strobe. Indication from the microcontroller that the current

bus cycle is a write operation.

5 Reserved - N Reserved for future use.

4 Reserved - N Reserved for future use.

3 INT1_L I Y Interrupt 1. Connected to the SCSI bus reset signal RST_L.

2 INT0_L I Y Interrupt 0. Connected to the 53C80S* SCSI chip interrupt.

1 Reserved - N Reserved for future use.

0 Reserved - N Reserved for future use.

Table 8-5: P3 Functions