OCPRF100 MP Server System Technical Product Specification

Revision 1.0

80

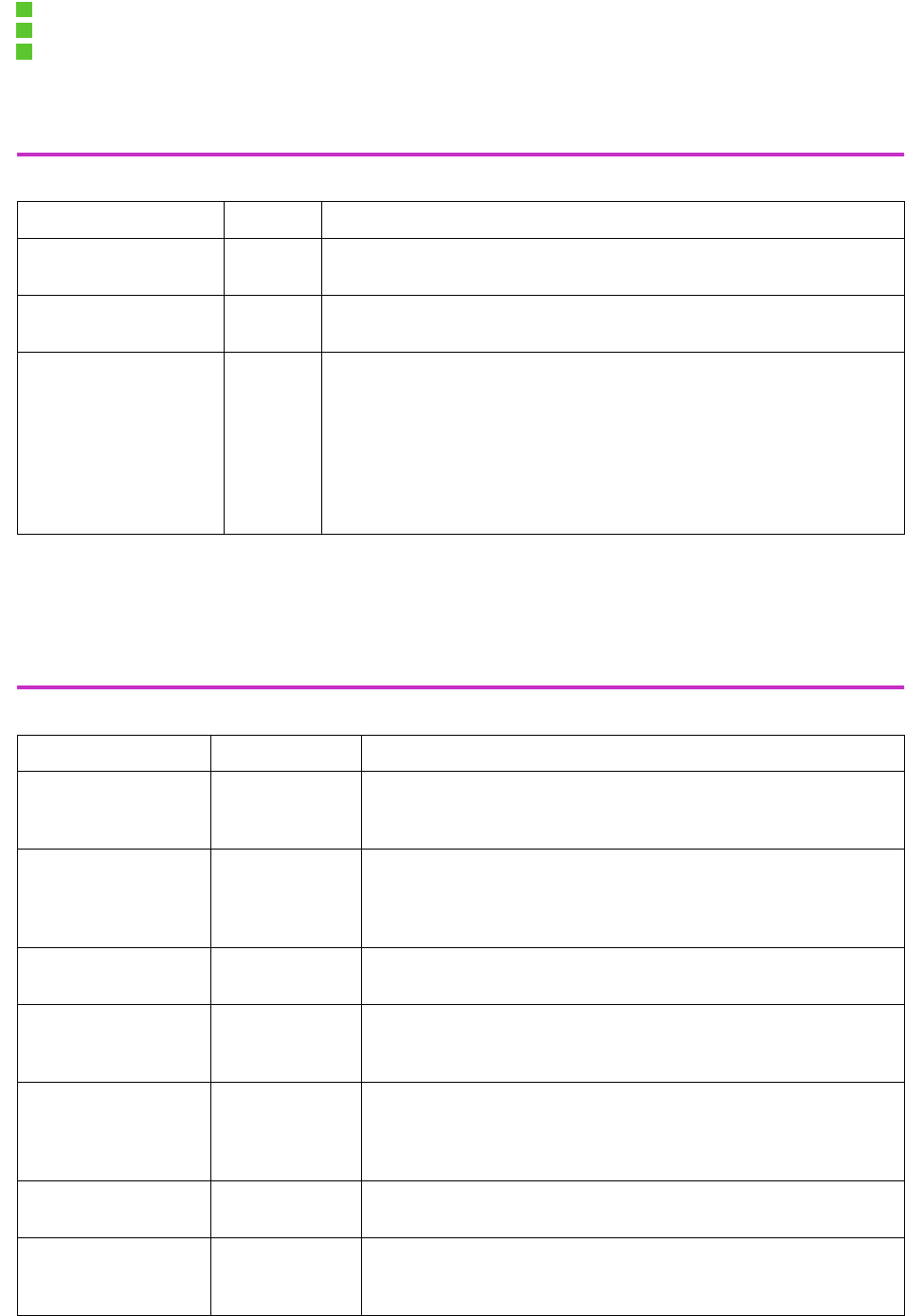

NOTES: Default values are marked with the "†" symbol.

Table 6-9: PCI Mode Submenu

Feature Option Description

Option ROM Scan Disabled

Enabled†

Enables option ROM scan.

Enable Master Disabled

Enabled†

Enables device(s) as a PCI bus master.

Latency Timer Default

0020h

0040h

0060h

0080h†

00A0h

00C0h

00E0h

Specifies the minimum guaranteed number of PCI bus clocks that a device

can master on a PCI bus during one transaction.

Table 6-10: I/O Device Configuration Submenu

Feature Option Description

Serial Port A Disabled

Enabled†

Auto

If set to “Auto,” BIOS configures the port.

Base I/O Address 3F8h†

2F8h

3E8h

2E8h

Selects the base I/O address for COM port A.

Interrupt IRQ 3

IRQ 4†

Selects the IRQ for COM port A.

Serial Port B Disabled

Enabled†

Auto

If set to “Auto,” BIOS configures the port.

Base I/O Address 3F8h

2F8h†

3E8h

2E8h

Selects the base I/O address for COM port B.

Interrupt IRQ 3†

IRQ 4

Selects the IRQ for COM port B.

Parallel Port Disabled

Enabled†

Auto

If set to “Auto,” BIOS configures the port.