83

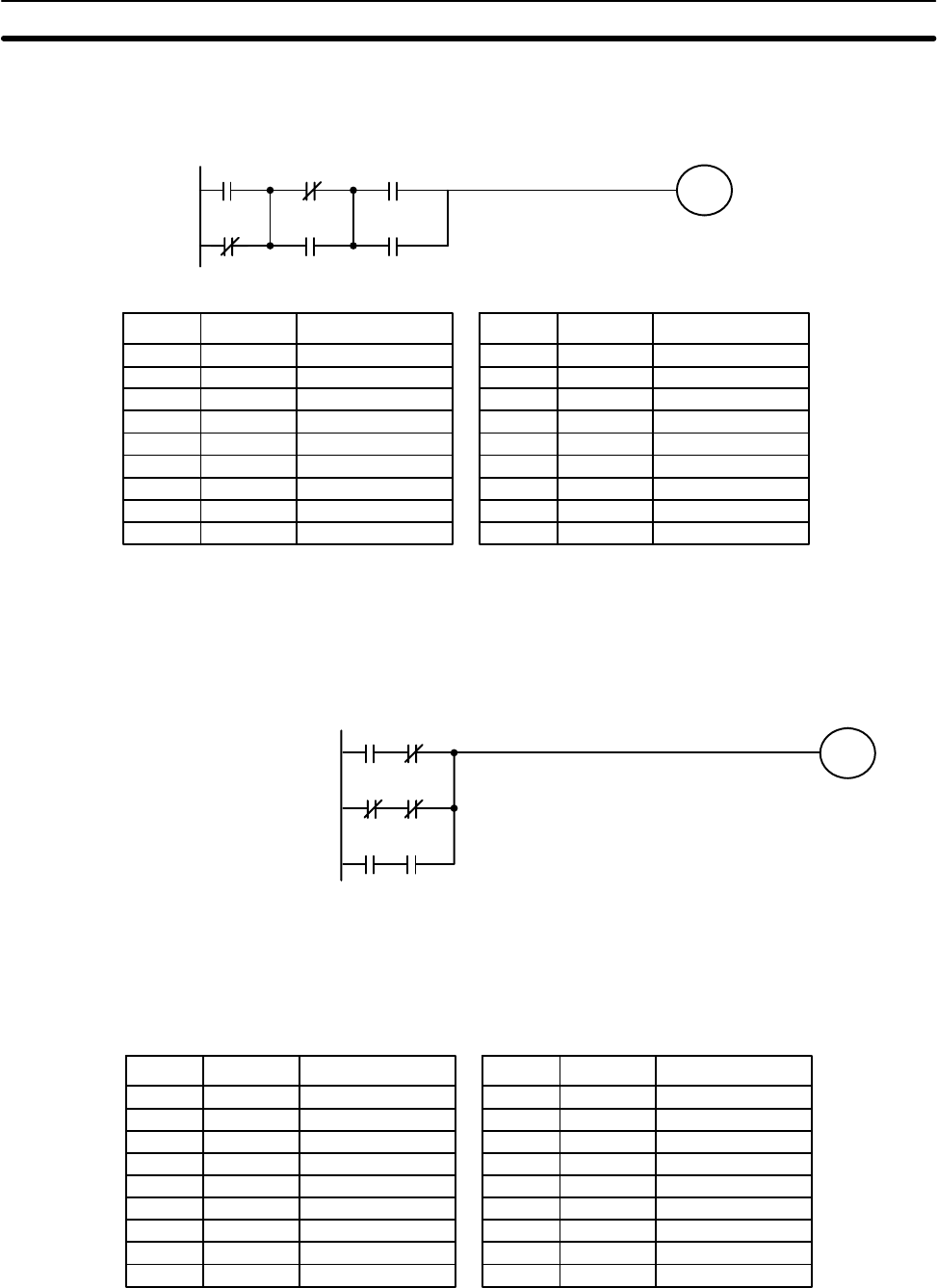

The following diagram requires AND LOAD to be converted to mnemonic code

because three pairs of parallel conditions lie in series. The two options for coding

the programs are also shown.

00000 00002 00004

00001 00003 00005

00500

Address Instruction Operands Address Instruction Operands

00000 LD 00000

00001 OR NOT 00001

00002 LD NOT 00002

00003 OR 00003

00004 AND LD —

00005 LD 00004

00006 OR 00005

00007 AND LD —

00008 OUT 00500

00000 LD 00000

00001 OR NOT 00001

00002 LD NOT 00002

00003 OR 00003

00004 LD 00004

00005 OR 00005

00006 AND LD —

00007 AND LD —

00008 OUT 00500

Again, with the method on the right, a maximum of eight blocks can be com-

bined. There is no limit to the number of blocks that can be combined with the

first method.

The following diagram requires OR LOAD instructions to be converted to mne-

monic code because three pairs of series conditions lie in parallel to each other.

00000 00001

00002 00003

00040 00005

00501

The first of each pair of conditions is converted to LOAD with the assigned bit

operand and then ANDed with the other condition. The first two blocks can be

coded first, followed by OR LOAD, the last block, and another OR LOAD; or the

three blocks can be coded first followed by two OR LOADs. The mnemonic

codes for both methods are shown below.

00000 LD 00000

00001 AND NOT 00001

00002 LD NOT 00002

00003 AND NOT 00003

00004 OR LD —

00005 LD 00004

00006 AND 00005

00007 OR LD —

00008 OUT 00501

00000 LD 00000

00001 AND NOT 00001

00002 LD NOT 00002

00003 AND NOT 00003

00004 LD 00004

00005 AND 00005

00006 OR LD —

00007 OR LD —

00008 OUT 00501

Address Instruction Operands Address Instruction Operands

Again, with the method on the right, a maximum of eight blocks can be com-

bined. There is no limit to the number of blocks that can be combined with the

first method.

Basic Ladder Diagrams Section 4-4