2 Troubleshooting Procedures 2.4 System Board Troubleshooting

2-24 [CONFIDENTIAL] QOSMIO F30 Maintenance Manual (960-555)

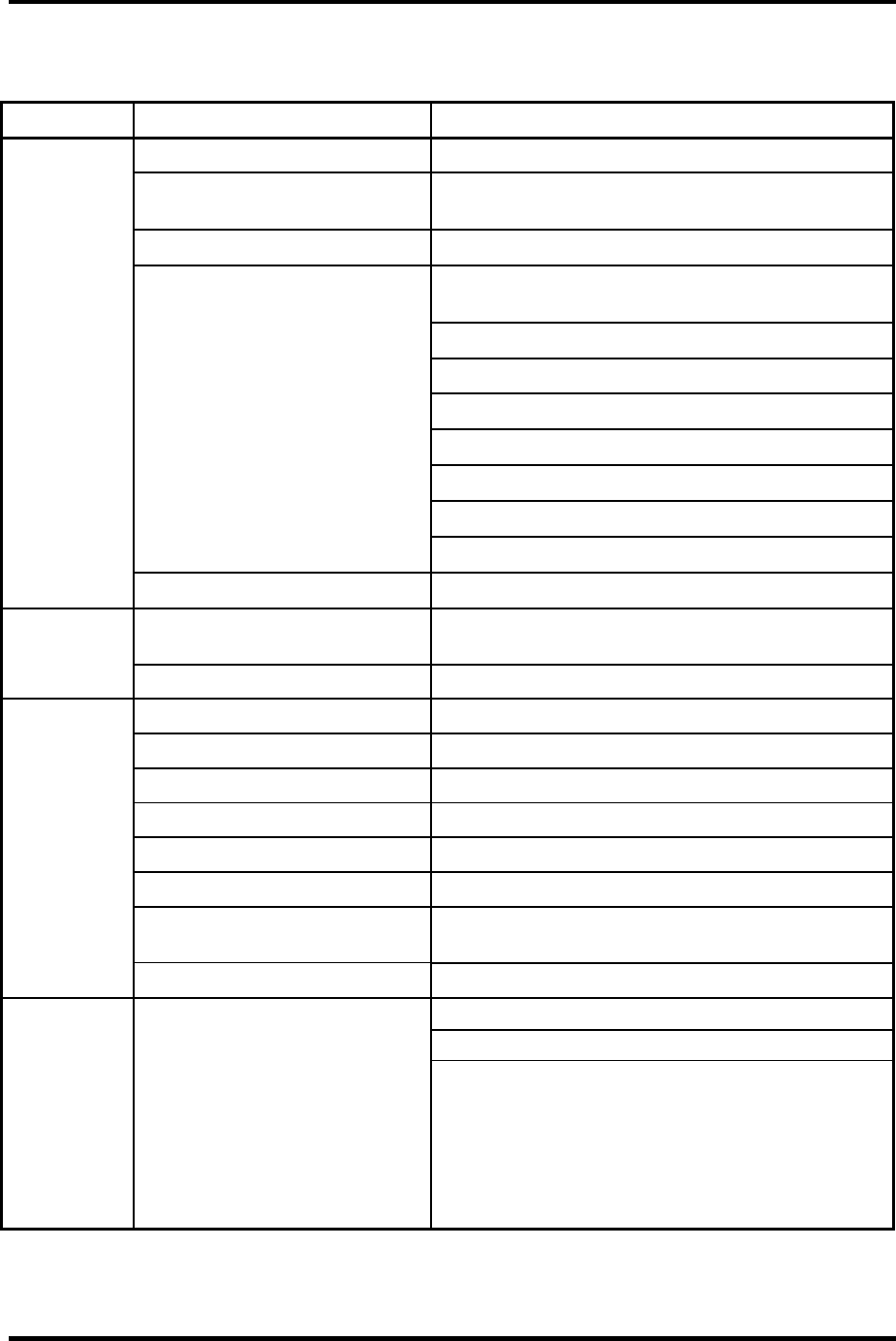

Table 2-4 Debug port (Boot mode) error status (3/10)

D port status Inspection items Details

Prohibition of cache

Permission of L1/L2 cache in

Flash ROM area

Update of microcode

Initialization of H/W (before

DRAM recognition)

Initialization of MCH

Initialization of ICH.D30.Func0

Initialization of ICH.D31.Func0

Initialization of ICH.D31.Func1/2

Initialization of USB Controller

Initialization of ICH.D31.Func3

Initialization of ICH Audio

F100h

Initialization of TI Controller

Initialization of PIT channel 1

(Setting the refresh interval to “30μs”)

Check of DRAM type and size

(at cold boot)

When unsupported memory is connected, becoming

HLT after beep sound (HLT when DRAM size is 0)

F101h

SM-RAM stack area test HLT When it can not be used as a stack

Cache configuration

Cache permission (L1/L2 Cache)

CMOS access test (at cold boot) (HLT when an error is detected)

Battery level check of CMOS

CMOS checksum check

Initialization of CMOS data (1)

Setting of IRT status (Setting of boot status and IRT busy flag, The rest bits

are 0)

F102h

Storing DRAM size in CMOS

Not resume when a CMOS error occurred

Not resume when resume status code is not set

Resume error check

S3 returning error (1CH) (Resume error =F17AH)

SM-RAM checksum check (Resume error =F173H)

Check of memory configuration change (Resume

error =F173H)

F103h Resume branch (at cold boot)

RAM area checksum check in system BIOS (Resume

error =F179H)