S1C63558 TECHNICAL MANUAL EPSON 155

CHAPTER 5: SUMMARY OF NOTES

(2)

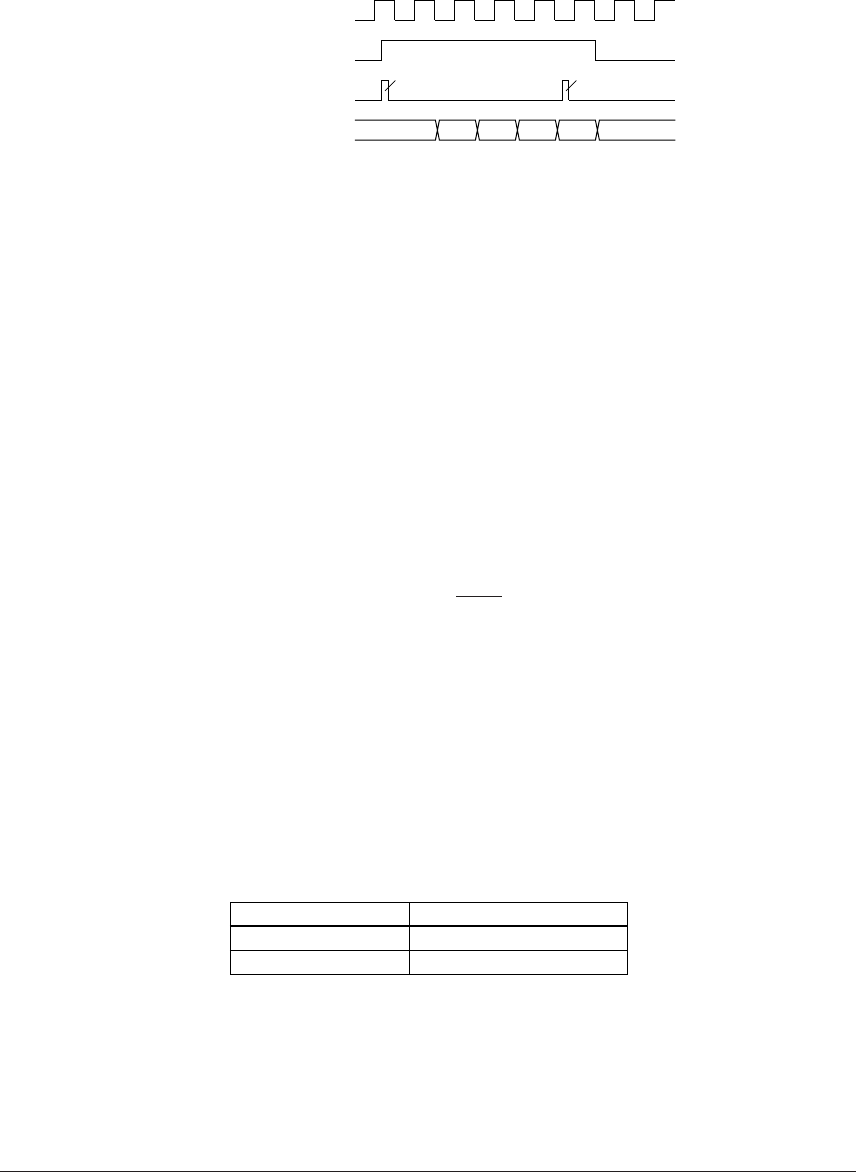

The programmable timer actually enters RUN/STOP status in synchronization with the falling edge of

the input clock after writing to the PTRUN0/PTRUN1 register. Consequently, when "0" is written to the

PTRUN0/PTRUN1 register, the timer enters STOP status at the point where the counter is decremented

(-1). The PTRUN0/PTRUN1 register maintains "1" for reading until the timer actually stops.

Figure 5.2.1 shows the timing chart for the RUN/STOP control.

PTRUN0/PTRUN1 (WR)

PTD0X/PTD1X 42H 41H 40H 3FH 3EH 3DH

PTRUN0/PTRUN1 (RD)

Input clock

"1" (RUN)

writing

"0" (STOP)

writing

Fig. 5.2.1 Timing chart for RUN/STOP control

It is the same even in the event counter mode. Therefore, be aware that the counter does not enter

RUN/STOP status if a clock is not input after setting the RUN/STOP control register (PTRUN0).

(3) Since the TOUT signal is generated asynchronously from the PTOUT register, a hazard within 1/2

cycle is generated when the signal is turned ON and OFF by setting the register.

(4) When the OSC3 oscillation clock is selected for the clock source, it is necessary to turn the OSC3

oscillation ON, prior to using the programmable timer. However the OSC3 oscillation circuit requires

a time at least 5 msec from turning the circuit ON until the oscillation stabilizes. Therefore, allow an

adequate interval from turning the OSC3 oscillation circuit ON to starting the programmable timer.

Refer to Section 4.3, "Oscillation Circuit", for the control and notes of the OSC3 oscillation circuit.

At initial reset, the OSC3 oscillation circuit is set in the OFF state.

Serial interface (1), (2)

(1) Be sure to initialize the serial interface mode in the transmit/receive disabled status (TXEN = RXEN =

"0").

(2) Do not perform double trigger (writing "1") to TXTRG (RXTRG) when the serial interface is in the

transmitting (receiving) operation.

(3) In the clock synchronous mode, since one clock line (SCLK) is shared for both transmitting and

receiving, transmitting and receiving cannot be performed simultaneously. (Half duplex only is

possible in clock synchronous mode.)

Consequently, be sure not to write "1" to RXTRG (TXTRG) when TXTRG (RXTRG) is "1".

(4) When a parity error or flaming error is generated during receiving in the asynchronous mode, the

receiving error interrupt factor flag ISER is set to "1" prior to the receive completion interrupt factor

flag ISRC for the time indicated in Table 4.11.10.1. Consequently, when an error is generated, you

should reset the receiving complete interrupt factor flag ISRC to "0" by providing a wait time in error

processing routines and similar routines.

When an overrun error is generated, the receiving complete interrupt factor flag ISRC is not set to "1"

and a receiving complete interrupt is not generated.

Table 5.2.1 Time difference between ISER and ISRC on error generation

Clock source Time difference

f

OSC3

/ n

Programmable timer

1/2 cycles of f

OSC3

/ n

1 cycle of timer 1 underflow

(5) When the demultiplied signal of the OSC3 oscillation circuit is made the clock source, it is necessary

to turn the OSC3 oscillation ON, prior to using the serial interface. A time interval of 5 msec, from the

turning ON of the OSC3 oscillation circuit to until the oscillation stabilizes, is necessary, due to the

oscillation element that is used. Consequently, you should allow an adequate waiting time after

turning ON of the OSC3 oscillation, before starting transmitting/receiving of serial interface.

(6) Be aware that the maximum clock frequency for the serial interface is limited to 1 MHz.