54 EPSON S1C63558 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (LCD Driver)

4.7.7 I/O memory of LCD driver

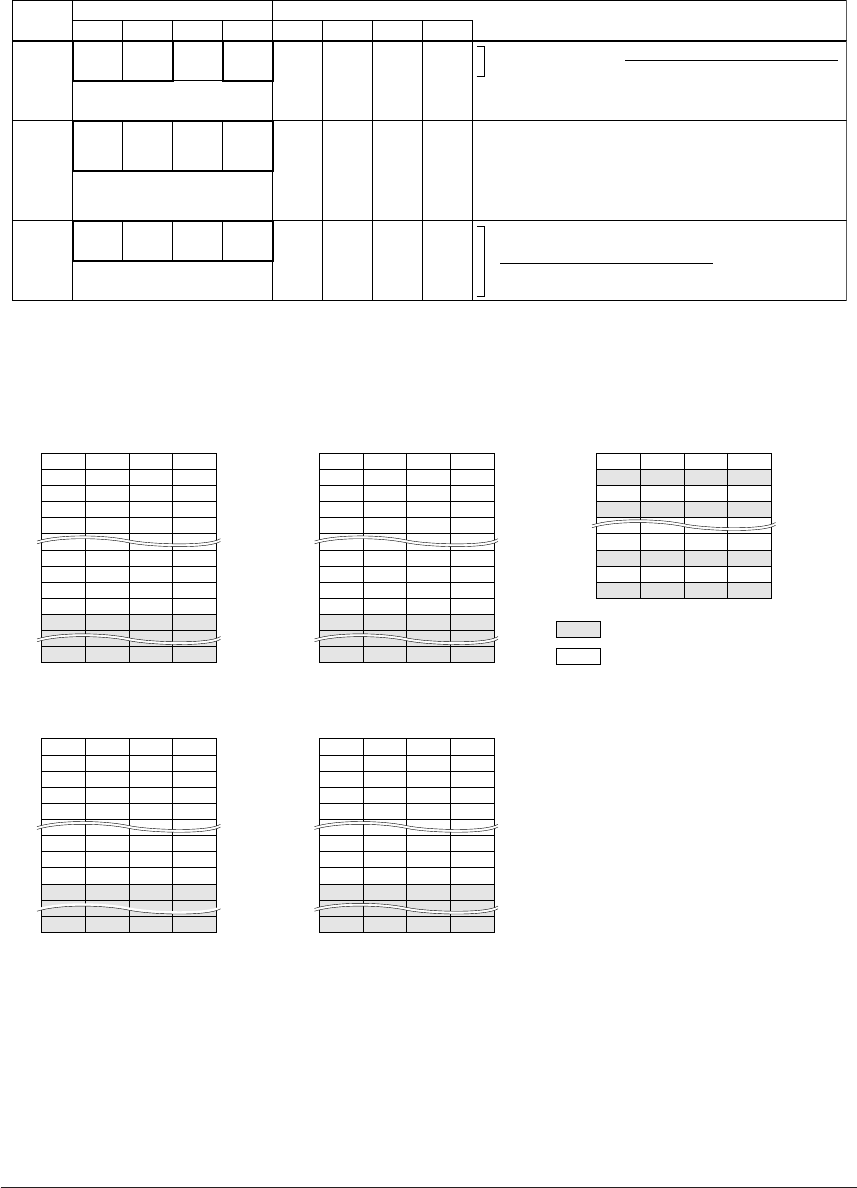

Table 4.7.7.1 shows the I/O addresses and the control bits for the LCD driver. Figure 4.7.7.1 shows the

display memory map.

Table 4.7.7.1 LCD driver control bits

Address Comment

D3 D2

Register

D1 D0 Name Init

∗1

10

FF60H

LDUTY1 LDUTY0 Dummy LPWR

R/W

LDUTY1

LDUTY0

Dummy

LPWR

0

0

0

0OnOff

LCD drive duty

switch

General-purpose register

LCD power On/Off

0

1/17

1

1/16

2, 3

1/8

[LDUTY1, 0]

Duty

FF61H

EXLCDC ALOFF ALON LPAGE

R/W

EXLCDC

ALOFF

ALON

LPAGE

0

1

0

0

Enable

All Off

All On

F100-F15F

Disable

Normal

Normal

F000-F05F

Expanded LCD driver signal control

LCD all Off control

LCD all On control

Display memory area selection (when 1/8 duty is selected)

General-purpose register when 1/16, 1/17 duty is selected

FF62H

LC3 LC2 LC1 LC0

R/W

LC3

LC2

LC1

LC0

–

∗

2

–

∗

2

–

∗

2

–

∗

2

0

Light

–

–

15

Dark

[LC3–0]

Contrast

LCD contrast adjustment

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

F000H

F001H

F002H

F003H

F004H

:

F04DH

F04EH

F04FH

F060H

:

F0FFH

D3

COM3

COM7

COM3

COM7

COM3

COM7

COM3

COM7

D2

COM2

COM6

COM2

COM6

COM2

COM6

COM2

COM6

D1

COM1

COM5

COM1

COM5

COM1

COM5

COM1

COM5

D0

COM0

COM4

COM0

COM4

COM0

COM4

COM0

COM4

SEG0

SEG0

SEG1

SEG1

SEG2

SEG38

SEG39

SEG39

Not-

implemented

COM0

–

COM7

F100H

F101H

F102H

F103H

F104H

:

F14DH

F14EH

F14FH

F160H

:

F1FFH

D3

COM11

COM15

COM11

COM15

COM11

COM15

COM11

COM15

D2

COM10

COM14

COM10

COM14

COM10

COM14

COM10

COM14

0

D1

COM09

COM13

COM09

COM13

COM9

COM13

COM9

COM13

D0

COM8

COM12

COM8

COM12

COM8

COM12

COM8

COM12

SEG0

SEG0

SEG1

SEG1

SEG2

SEG38

SEG39

SEG39

Not-

implemented

COM8

–

COM15

(a) When 40 × 17 is selected

F000H

F001H

F002H

F003H

F004H

:

F05DH

F05EH

F05FH

F060H

:

F0FFH

D3

COM3

COM7

COM3

COM7

COM3

COM7

COM3

COM7

D2

COM2

COM6

COM2

COM6

COM2

COM6

COM2

COM6

D1

COM1

COM5

COM1

COM5

COM1

COM5

COM1

COM5

D0

COM0

COM4

COM0

COM4

COM0

COM4

COM0

COM4

SEG0

SEG0

SEG1

SEG1

SEG2

SEG46

SEG47

SEG47

Not-

implemented

COM0

–

COM7

F100H

F101H

F102H

F103H

F104H

:

F15DH

F15EH

F15FH

F160H

:

F1FFH

D3

COM3

COM7

COM3

COM7

COM3

COM7

COM3

COM7

D2

COM2

COM6

COM2

COM6

COM2

COM6

COM2

COM6

D1

COM1

COM5

COM1

COM5

COM1

COM5

COM1

COM5

D0

COM0

COM4

COM0

COM4

COM0

COM4

COM0

COM4

SEG0

SEG0

SEG1

SEG1

SEG2

SEG46

SEG47

SEG47

Not-

implemented

COM0

–

COM7

(b) When 48 × 8 is selected

F200H

F201H

F202H

F203H

:

F24CH

F24DH

F24EH

F24FH

D3

0

0

0

0

D2

0

0

0

0

D1

0

0

0

0

D0

COM16

COM16

COM16

COM16

SEG0

SEG1

SEG38

SEG39

COM16

Unused area Always "0"

No Operation

Reading:

Writing:

Non-implementation area Read/write disabled

Fig. 4.7.7.1 Display memory map