82575 Ethernet Controller Design Guide

22

3.5 82575 Ethernet Controller Device Test Capability

The 82575 Ethernet Controller Gigabit Ethernet Controller contains a test access port

(3.3 V only) conforming to the IEEE 1149.1a-1994 (JTAG) Boundary Scan specification.

To use the test access port, connect these balls to pads accessible by your test

equipment.

A BSDL (Boundary Scan Definition Language) file describing the 82575 Ethernet

Controller device is available for use in your test environment.

The controller also contains an XOR test tree mechanism for simple board tests. Details

of XOR tree operation are available from your Intel representative.

Information about how to obtain test models is available from your Intel

representative.

3.6 PHY Functionality

This section describes various functions of the PHY.

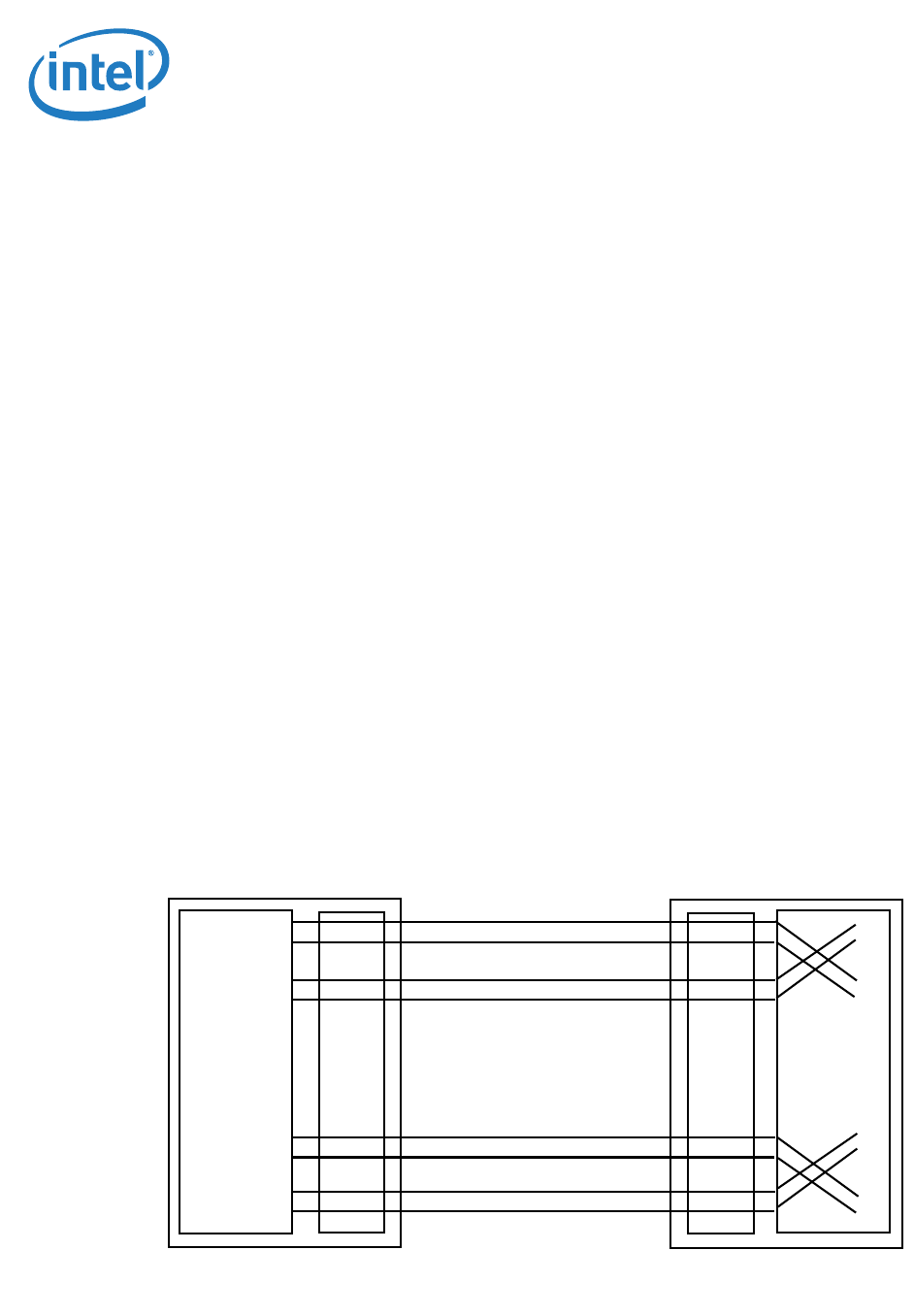

3.6.1 Auto Cross-over for MDI and MDI-X resolution

Twisted pair Ethernet PHY's must be correctly configured for MDI or MDI-X operation to

interoperate. The PHY supports the automatic MDI/MDI-X configuration; manual (non-

automatic) configuration is still possible by special cable, etc.

For 1000BASE-T links, pair identification is determined automatically in accordance

with the standard.

For 10/100 links and during auto-negotiation, pair usage is determined by Bits 12 and

13 in the Port Control Register (PHYREG18).

In addition, the PHY has an Automatic Crossover Detection function. If Bit 18.12 = 1,

the PHY automatically detects which application is being used and configures itself

accordingly

A

B

C

D

TX

RX

RX

TX

RJ45

RJ45

TX

TX

RX

RX

TX

TX

RX

RX

PHY

Flat Cable

TX

TX

RX

RX

A

B

C

D

MDI (DTE/NIC)

MDIX (switch)

Cross (1:0)=00

Cross (1:0)=01