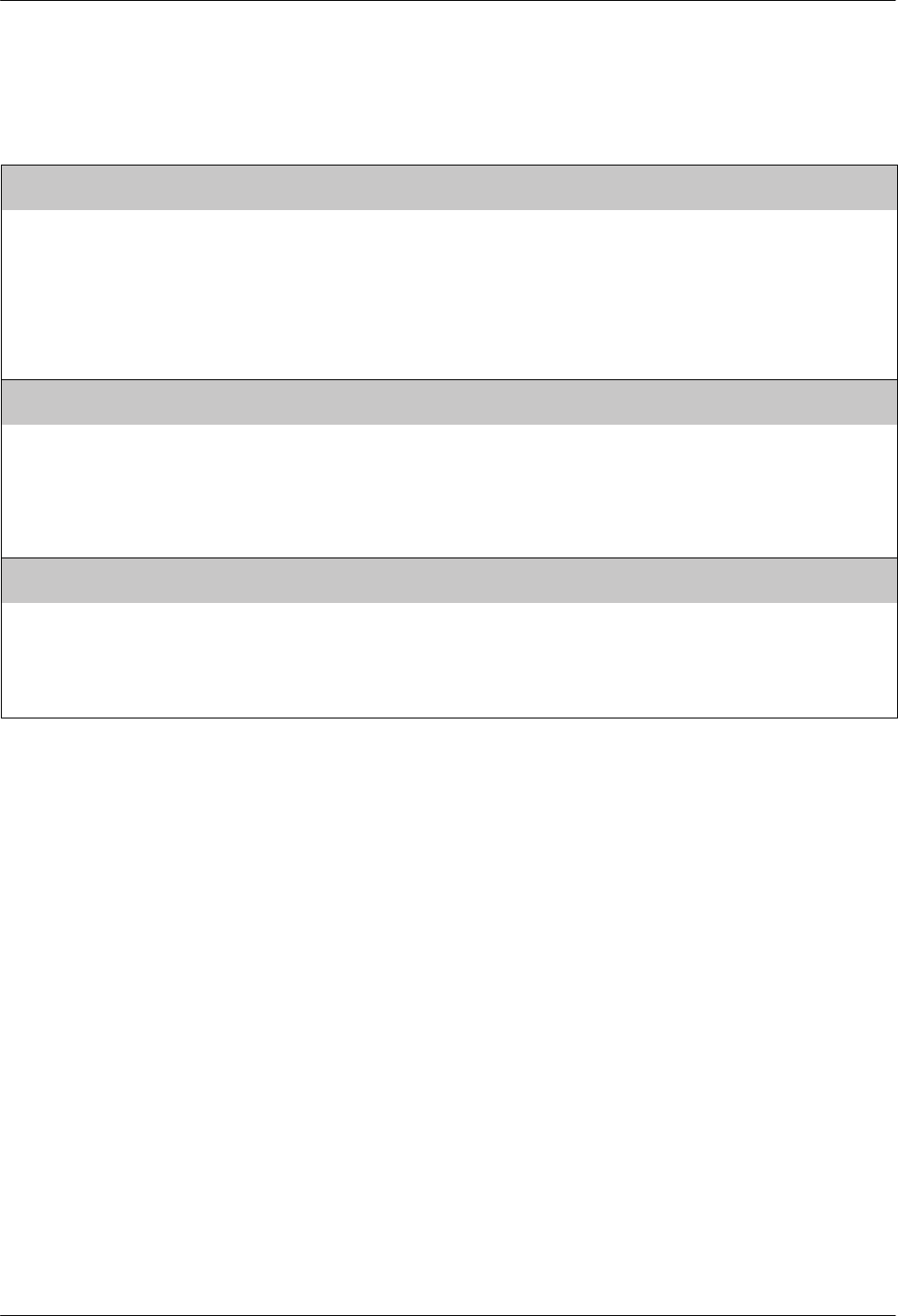

ACCULINK 316x DSU/CSU

C-6 December 1996 3160-A2-GB22-10

Table C-2

(3 of 3)

Port Configuration Options

Tx Clock: Int

Next Int Ext Prev

Data Port Transmit Clock. Specifies whether the transmitted data for the port is clocked using an internal clock provided

by the DSU/CSU (synchronized to the clock source specified by the Clock Src General configuration option) or an

external clock provided by the DTE connected to the port. When an external clock is used, it must be synchronized to the

same clock source as the DSU/CSU.

Int – Indicates the clock is provided internally by the DCE on the TXC interchange circuit DB (CCITT 114) – Transmit

Signal Element Timing.

Ext – Indicates the clock is provided externally by the DTE on the XTXC interchange circuit DA (CCITT 113) – Transmit

Signal Element Timing.

Invert TxC: Disab

Next Enab Disab Prev

Invert Transmit Clock. Specifies whether the clock supplied by the DCE on interchange circuit DB (CCITT 114) – Transmit

Signal Element Timing (DCE source) TXC is phase inverted with respect to interchange circuit BA (CCITT 103) –

Transmitted Data (TD). This option is useful when long cable lengths between the DSU/CSU and the DTE are causing

data errors.

Enab – Indicates the clock supplied by the DCE on TXC for this port is phase inverted.

Disab – Indicates the clock supplied by the DCE on TXC for this port is not inverted.

Invert Data: Disab

Next Enab Disab Prev

Invert Transmit and Received Data. Specifies whether the transmitted and received data for the port is logically inverted

before being transmitted or received from the network. This configuration option is useful for applications where HDLC

data is being transported whereby inverting the data ensures density requirements for the Network Interface are met.

Enab – Indicates the transmitted and received data for this port is logically inverted.

Disab – Indicates the transmitted and received data for this port is not inverted.