119

STP2002QFP

Fast Ethernet, Parallel Port, SCSI (FEPS) - STP2002QFP

Sun Microsystems,

7.5.42 TX_MAC Defer Timer

7.5.43 TX_MAC Normal Collision Counter

7.5.44 TX_MAC First Successful Collision Counter

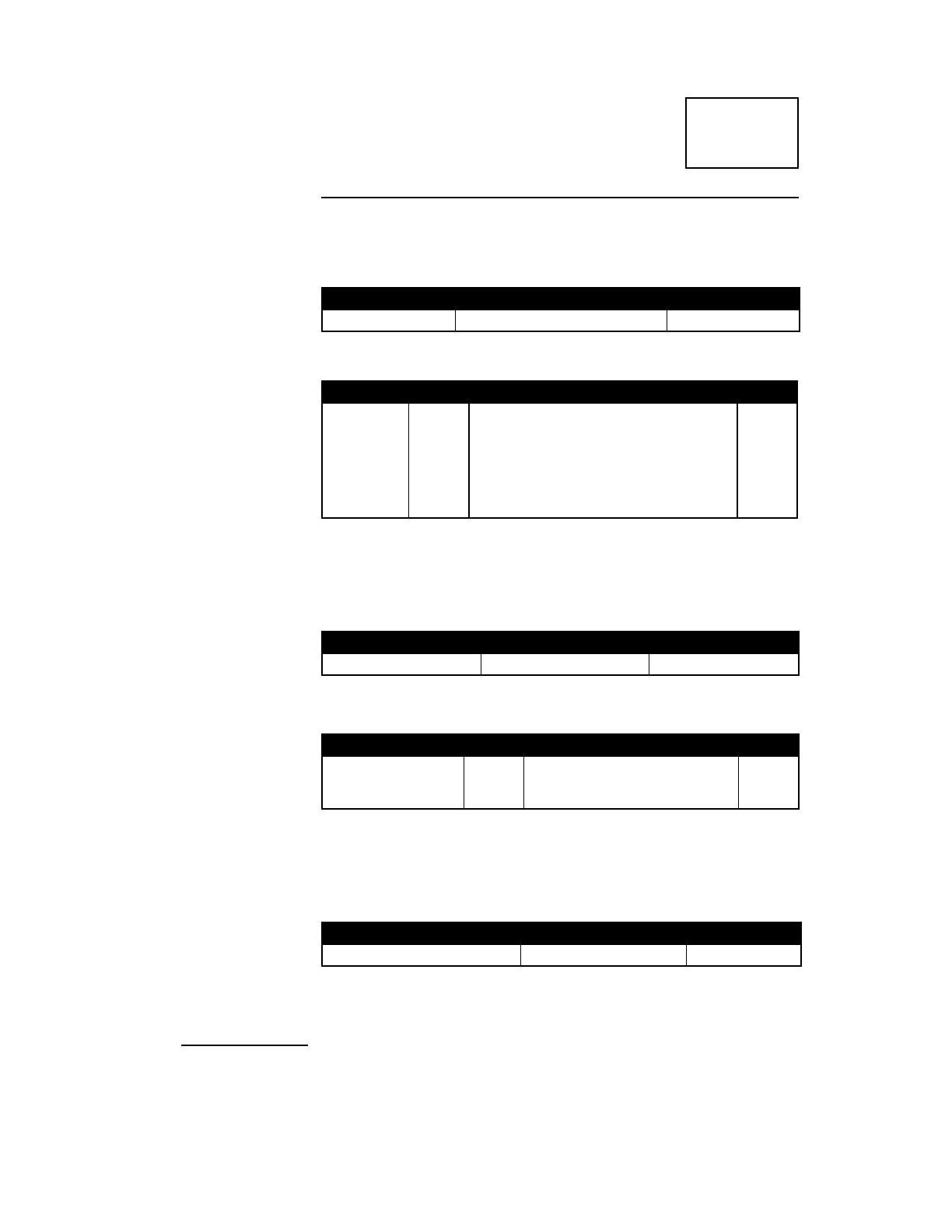

Table 167: TX_MAC Defer Timer Address

Register Physical Address Access Size

Defer timer 0x8C0_623C 4 bytes

Table 168: TX_MAC Defer Timer Definition

Field Bits Description Type

Defer timer 15:0 Loadable timer increments when the TX_MAC is

deferring to traffic on the network while it is

attempting to transmit a frame. The time base for the

timer is the media byte clock divided by 256. Thus,

on a 10-Mbps network the timer ticks are 200 msec,

and on a 100-Mbps network the timer ticks are 20

msec.

R/W

Table 169: TX_MAC Normal Collision Counter Address

Register Physical Address Access Size

Normal collision counter 0x8C0_6240 4 bytes

Table 170: TX_MAC Normal Collision Counter Definition

Field Bits Description Type

Normal collision counter 15:0 Loadable counter, increments for every

frame transmission attempt that experi-

ences a collision.

R/W

Table 171: TX_MAC First Successful Collision Counter Address

Register Physical Address Access Size

First successful collision counter 0x8C0_6244 4 bytes